| M                                         | cron                                                                                           | 512M                    | 1B, 1GB,                 | 2GB, 4G                                   | B (x64, E                                | DR) 240-F | Pin DDR2                     | 2 SDRAM                      | UDIN<br>Featu          |

|-------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------|--------------------------|-------------------------------------------|------------------------------------------|-----------|------------------------------|------------------------------|------------------------|

| 1T16H1<br>1T16H1                          | F6464A – 512<br>F12864A – 1G<br>F25664A – 2G                                                   | B                       |                          |                                           |                                          |           |                              |                              |                        |

|                                           | F51264A – 4G<br>nent data sheets, ref<br>Key Timing Pa                                         | er to Micron            |                          |                                           |                                          |           |                              |                              |                        |

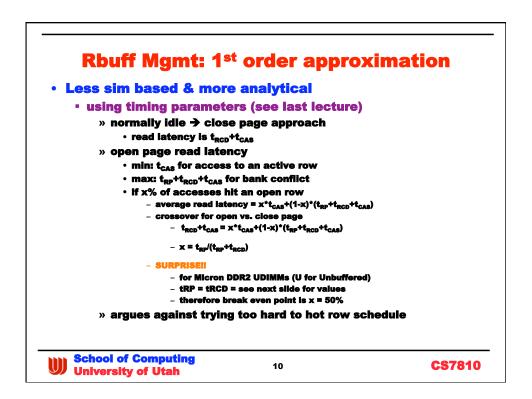

| able 1:                                   | Key Timing Pa                                                                                  | er to Micron            | Da                       | ta Rate (M                                | ſ/s)                                     | CI = 2    | tRCD                         | t <sub>RP</sub>              | t <sub>RC</sub>        |

| able 1:                                   | Key Timing P                                                                                   | er to Micron            |                          |                                           |                                          | CL = 3    | tRCD<br>(ns)                 | t <sub>RP</sub><br>(ns)      | t <sub>R(</sub><br>(ns |

| able 1:<br>Speed<br>Grade                 | Key Timing Pa<br>Industry<br>Nomenclature                                                      | arameters               | Da<br>CL = 6             | ta Rate (M<br>CL = 5                      | T/s)<br>CL = 4                           |           | (ns)                         | (ns)                         | (rns                   |

| able 1:<br>Speed<br>Grade<br>-1GA         | Normenciature<br>PC2-8500                                                                      | arameters               | Da<br>CL = 6             | ta Rate (M<br>CL = 5<br>667               | Г/s)<br>CL = 4<br>-                      | -         | (ns)<br>13.125               | (ns)<br>13.125               | (ns<br>54              |

| able 1:<br>Speed<br>Grade<br>-1GA<br>-80E | Key Timing Pa<br>Industry<br>Normenclature<br>PC2-8500<br>PC2-6400                             | arameters CL = 7 1066 - | Da<br>CL = 6<br>800<br>- | ta Rate (M<br>CL = 5<br>667<br>800        | <b>T/s)</b><br><b>CL = 4</b><br>-<br>533 | -         | (ns)<br>13.125<br>12.5       | (ns)<br>13.125<br>12.5       | (ns<br>54<br>55        |

| speed<br>Grade<br>-1GA<br>-80E<br>-800    | Key Timing P:<br>Key Timing P:<br>Industry<br>Nomenclature<br>PC2-8500<br>PC2-6400<br>PC2-6400 | CL = 7<br>1066<br>-     | Da<br>CL = 6<br>800<br>- | ta Rate (M<br>CL = 5<br>667<br>800<br>667 | T/s)<br>CL = 4<br>-<br>533<br>533        |           | (ns)<br>13.125<br>12.5<br>15 | (ns)<br>13.125<br>12.5<br>15 | (ns<br>54<br>55<br>55  |

| • Per | formance isn't everything                                              |                      |                 |              |

|-------|------------------------------------------------------------------------|----------------------|-----------------|--------------|

| - 6   | ower is topping the charts the                                         | ese davs             |                 |              |

|       | onsider a RDRAM system                                                 |                      |                 |              |

|       | » 16 x 256 Mbit Direct RDRAM de                                        | avices               |                 |              |

|       | • 3 modes                                                              |                      |                 |              |

|       | - active (all banks active)                                            |                      |                 |              |

|       | - standby (active but takes long                                       | er to bring back     | to active an    | d then read) |

|       | <ul> <li>NAP (inactive banks so row ac</li> </ul>                      | cess must be re      | done)           |              |

|       |                                                                        |                      |                 |              |

|       |                                                                        |                      |                 |              |

|       |                                                                        |                      |                 |              |

|       | Condition                                                              | Current mA           | Relative        |              |

|       | 1 device read active, 15 in NAP                                        | 1195                 | 1               |              |

|       | 1 device read active, 15 in NAP<br>1 device read active, 15 in standby | 1195<br>2548         | 1<br>2.1        |              |

|       | 1 device read active, 15 in NAP                                        | 1195                 | 1               |              |

|       | 1 device read active, 15 in NAP<br>1 device read active, 15 in standby | 1195<br>2548         | 1<br>2.1        |              |

|       | 1 device read active, 15 in NAP<br>1 device read active, 15 in standby | 1195<br>2548<br>3206 | 1<br>2.1<br>2.7 |              |

| Alternat                                    | tive Viewpoi               | nts                  |

|---------------------------------------------|----------------------------|----------------------|

| • Impulse (Utah)                            |                            |                      |

| <ul> <li>use an extra level of i</li> </ul> | indirection to supp        | ort multiple strides |

| » get the cache line y                      | ou want                    |                      |

| <ul> <li>not just the contigu</li> </ul>    | uous block that you usua   | ally get             |

| » use shadow memory                         | (not in the physical       | address map)         |

|                                             | gets for user defined acc  | •                    |

|                                             | s based on strides in pla  | У                    |

| » memory controller                         |                            |                      |

| • controls map to mi                        | nimize dank contlict       |                      |

| FB-Dimm                                     |                            |                      |

| <ul> <li>on DIMM ASIC could be</li> </ul>   | be impulse like            |                      |

| » each DIMM is a chai                       | nnel                       |                      |

| » Impulse like game c                       | ould be played             |                      |

| <ul> <li>albeit with a bit mo</li> </ul>    | ore control logic in the A | MB chip              |

| School of Computing                         |                            |                      |

|                                             | 14                         | CS781(               |

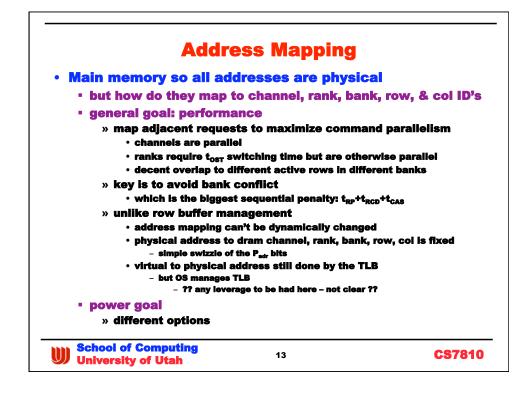

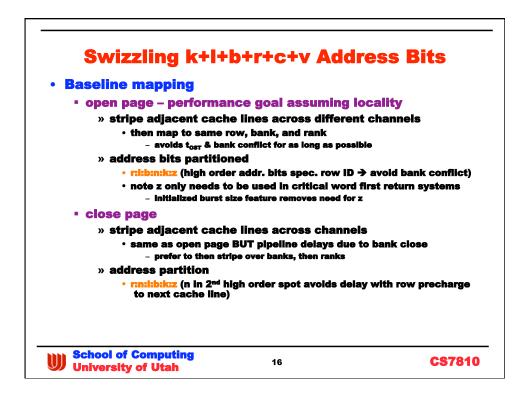

| Symbol | Variable Dependence                                                                        | Description               |

|--------|--------------------------------------------------------------------------------------------|---------------------------|

| K      | Independent                                                                                | # of channels in system   |

| L      | Independent                                                                                | # of ranks per channel    |

| B      | Independent                                                                                | # of banks per rank       |

| R      | Independent                                                                                | # of rows per bank        |

| С      | Independent                                                                                | # of columns per row      |

| V      | Independent                                                                                | # of bytes per column     |

| z      | Independent                                                                                | # of bytes per cache line |

| N      | Dependent                                                                                  | # of cache lines per row  |

|        | ory Capacity = K*L*B*R<br>& CV= NZ (since we care                                          |                           |

|        | Since we're whacked o<br>L =2', B=2 <sup>b</sup> , etc. for sim<br>non powers of 2 could b | •                         |

|        | f Computing<br>y of Utah                                                                   | 5 <b>C\$7810</b>          |

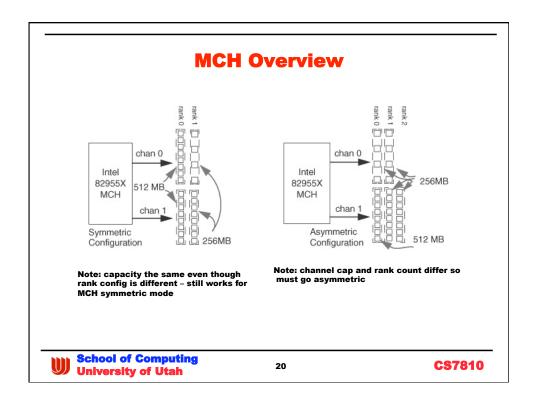

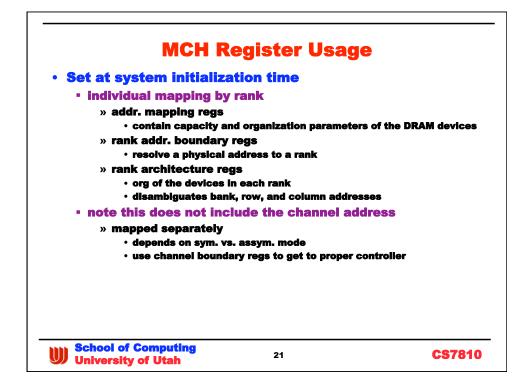

|                    | Example: Intel 82955X MCH                                                           |                                        |                            |                           |                          |                          |                            |

|--------------------|-------------------------------------------------------------------------------------|----------------------------------------|----------------------------|---------------------------|--------------------------|--------------------------|----------------------------|

| - 2                | H = memory c<br>2 memory contr<br>> each indepen<br>• each chann<br>bossible rank c | rollers<br>idently con<br>nel supports | trol 2 DDR<br>up to 4 rani |                           | neis                     |                          |                            |

| Rank<br>Cap.<br>MB | Config<br>banks,<br>rows,cois,<br>coisize                                           | Rank<br>dev.cap x<br>dev.cnt           | Rank<br>config<br>BxRxCxV  | Bank<br>Addr<br>bits<br>b | Row<br>Addr<br>bits<br>r | Col<br>Addr<br>bits<br>c | Col<br>Addr<br>Offset<br>V |

| 128                | 4x8192x512x2                                                                        | 256 Mb x 4                             | 4x8192x51<br>2x8           | 2                         | 13                       | 9                        | 3                          |

| 256                | 4x8192x1024x2                                                                       | 512 Mb x 4                             | 4x8192x<br>1024x8          | 2                         | 13                       | 10                       | 3                          |

| 256                | 4x8192x1024x1                                                                       | 256 Mb x 8                             | 4x8192x<br>1024x8          | 2                         | 13                       | 10                       | 3                          |

| 512                | 8x8192x1024x2                                                                       | 1 Gb x 4                               | 8x8192x<br>1024x8          | 2                         | 13                       | 10                       | 3                          |

| 512                | 4x16384x1024x1                                                                      | 512 Mb x 4                             | 4x16384x<br>1024x8         | 2                         | 14                       | 10                       | 3                          |

| <ul> <li>sual benefit</li> <li>writes are not typically critica</li> <li>» defer if it helps the schedule</li> <li>still have to check the cache of</li> <li>» adds some complexity</li> <li>» also delays read if conservative</li> <li>• e.g. check cache and then go</li> <li>• wise choice in power constrait</li> <li>- go eager otherwise</li> </ul> | on a RAW access pattern<br>re<br>to DRAM |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| <ul> <li>» defer if it helps the schedule</li> <li>still have to check the cache of</li> <li>» adds some complexity</li> <li>» also delays read if conservative</li> <li>• e.g. check cache and then go</li> <li>• wise choice in power constrain</li> <li>- go eager otherwise</li> </ul>                                                                 | on a RAW access pattern<br>re<br>to DRAM |

| <ul> <li>still have to check the cache of<br/>» adds some complexity         » also delays read if conservativ<br/>• e.g. check cache and then go         • wise choice in power constrail<br/>– go eager otherwise         </li> </ul>                                                                                                                    | re<br>to DRAM                            |

| <ul> <li>» adds some complexity</li> <li>» also delays read if conservative</li> <li>• e.g. check cache and then go</li> <li>• wise choice in power constrait</li> <li>– go eager otherwise</li> </ul>                                                                                                                                                     | re<br>to DRAM                            |

| <ul> <li>» also delays read if conservative</li> <li>• e.g. check cache and then go</li> <li>• wise choice in power constrait</li> <li>– go eager otherwise</li> </ul>                                                                                                                                                                                     | to DRAM                                  |

| <ul> <li>e.g. check cache and then go</li> <li>wise choice in power constrai</li> <li>go eager otherwise</li> </ul>                                                                                                                                                                                                                                        | to DRAM                                  |

| • wise choice in power constrai<br>– go eager otherwise                                                                                                                                                                                                                                                                                                    |                                          |

| – go eager otherwise                                                                                                                                                                                                                                                                                                                                       |                                          |

| RAM specific benefit                                                                                                                                                                                                                                                                                                                                       |                                          |

|                                                                                                                                                                                                                                                                                                                                                            |                                          |

| high speed buses take time to                                                                                                                                                                                                                                                                                                                              | turn around                              |

| » bigger issue in DDRx where x>                                                                                                                                                                                                                                                                                                                            | =2 land                                  |

| » hence RWRWRW transaction                                                                                                                                                                                                                                                                                                                                 | s are slow                               |

| use                                                                                                                                                                                                                                                                                                                                                        |                                          |

| common in XDR based RDRAM                                                                                                                                                                                                                                                                                                                                  | systems                                  |

| <ul> <li>Intel i8870 controller does it feel</li> </ul>                                                                                                                                                                                                                                                                                                    | or JEDEC systems                         |