| FB Dimm Idea                                                                             |        |

|------------------------------------------------------------------------------------------|--------|

| <ul> <li>Need to create higher bandwidth</li> </ul>                                      |        |

| • DDR2                                                                                   |        |

| » 400 MT/s configured <ul> <li>• up to 4 two-rank DIMM's</li> </ul>                      |        |

| • DDR3                                                                                   |        |

| » 800 MT/s configured<br>• 1 2-rank Dimm                                                 |        |

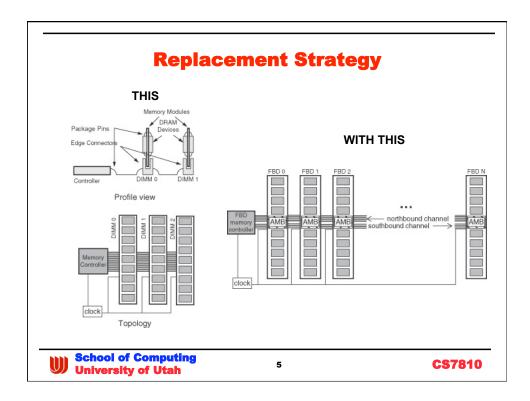

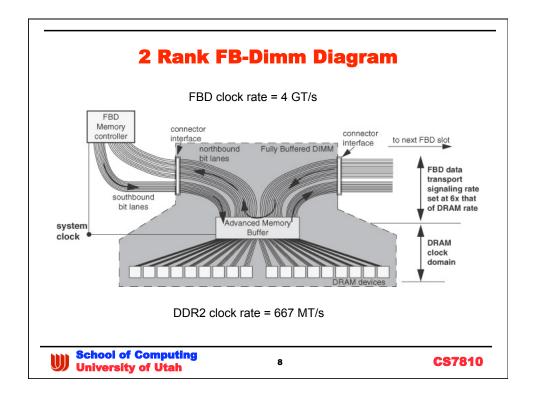

| <ul> <li>Move multi-drop bus to the DIMM</li> </ul>                                      |        |

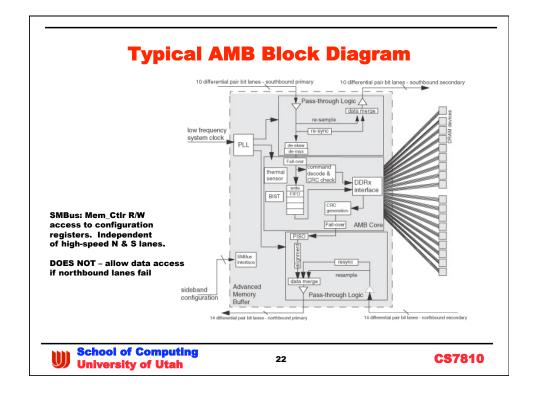

| • daisy chain the DIMMs using an AMB ASIC                                                |        |

| » AMB ::= Advanced Memory Buffer                                                         |        |

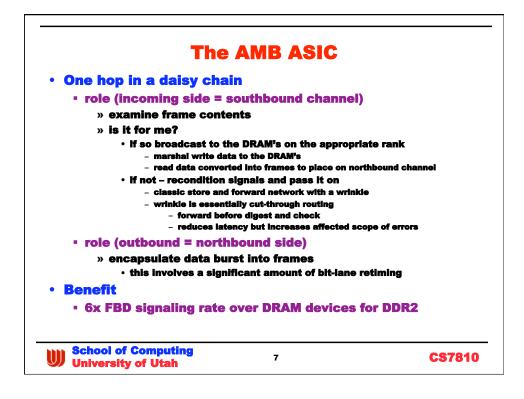

| actually much more than a buffer                                                         |        |

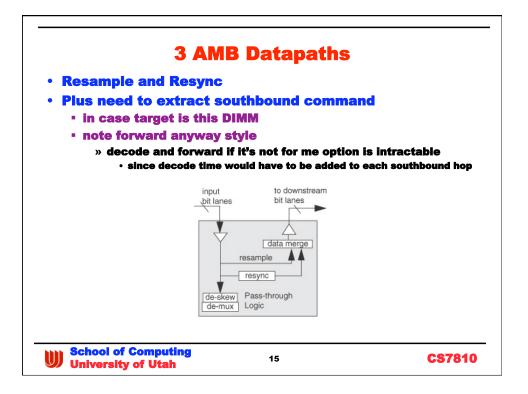

| <ul> <li>also does bit-lane retiming</li> <li>packetized frame-relay protocol</li> </ul> |        |

| » AMD duties                                                                             |        |

| <ul> <li>extract DRAM commands from frame</li> </ul>                                     |        |

| • control DRAM devices (2ndary mem.ctir)                                                 |        |

| School of Computing                                                                      |        |

| School of Computing                                                                      | CS7810 |

| Commands                                                    |                                                                  |                          |  |  |

|-------------------------------------------------------------|------------------------------------------------------------------|--------------------------|--|--|

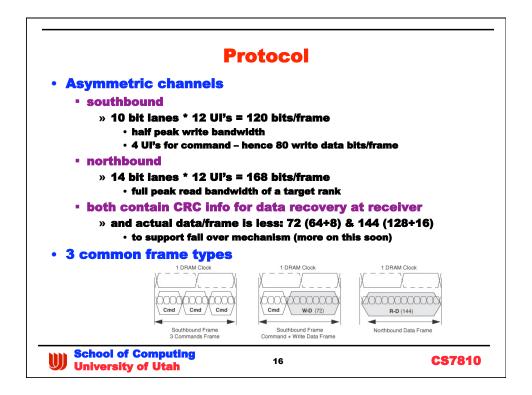

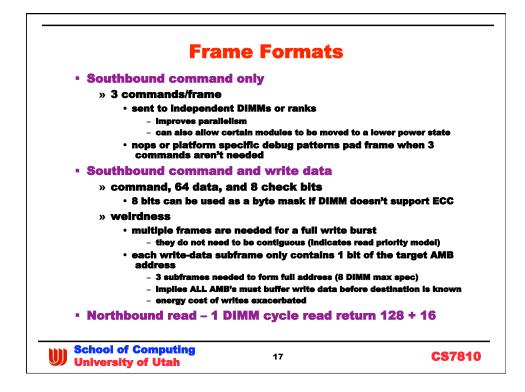

| • 2 types                                                   |                                                                  |                          |  |  |

| <ul> <li>channel</li> </ul>                                 |                                                                  |                          |  |  |

| » manage the AMB's                                          |                                                                  |                          |  |  |

| • debug                                                     |                                                                  |                          |  |  |

| <ul> <li>read and write con</li> </ul>                      | figuration register                                              |                          |  |  |

| <ul> <li>clock enable mana</li> </ul>                       | igement                                                          |                          |  |  |

| <ul> <li>soft channel reset</li> </ul>                      |                                                                  |                          |  |  |

|                                                             | transmission error is detecte                                    | =                        |  |  |

| _                                                           | letects CRC error or AMB sign<br>etry all writes that weren't co |                          |  |  |

| <ul> <li>reset and then re</li> <li>channel sync</li> </ul> | etry all writes that weren't co                                  | mmittea                  |  |  |

| -                                                           | clock recovery circuits see t                                    | he min. # of transitions |  |  |

|                                                             | d – transitions provided by mo                                   |                          |  |  |

| – northbound                                                | i response – last DIMM sends                                     | fake read return         |  |  |

|                                                             | d once every 42-46 frames (Ji                                    |                          |  |  |

| -                                                           | can't be powered down easily                                     | y (another power defect) |  |  |

| • DRAM                                                      |                                                                  |                          |  |  |

| » AMB's decode and s                                        | end to DRAM devices                                              | on the DIMM              |  |  |

|                                                             |                                                                  |                          |  |  |

| School of Computing                                         |                                                                  | C\$7810                  |  |  |

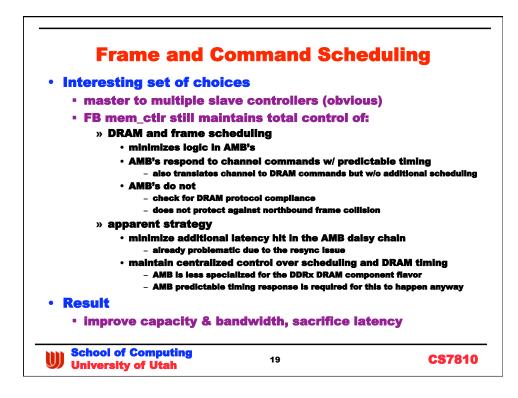

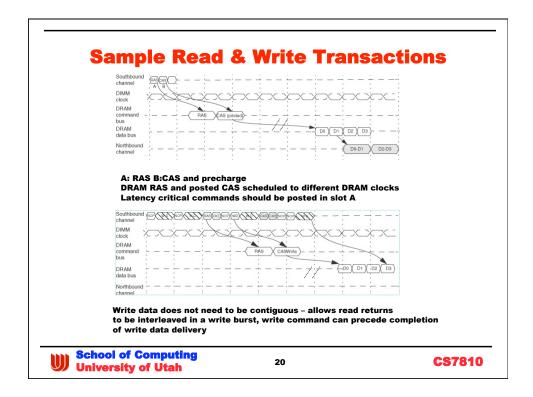

|                                     |             |             | FB Dimm Per                      | formance                                                                                      |

|-------------------------------------|-------------|-------------|----------------------------------|-----------------------------------------------------------------------------------------------|

| Component                           | Min<br>(ps) | Max<br>(ps) | Notes                            | Postboard To detential get bit interes                                                        |

| A: Ctrlr to<br>DIMM flight          | 800         | 1200        | routing distance dependent       | Serialization                                                                                 |

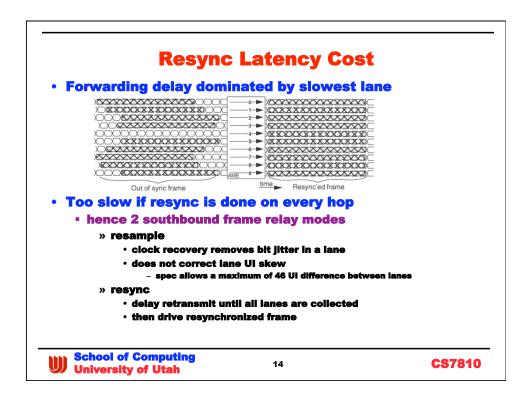

| B: SB frame<br>resample             | 900         | 1600        | process dependent                | Pass-through Logic                                                                            |

| C: SB DIMM-<br>DIMM flight          | 600         | 900         | routing distance dependent       |                                                                                               |

| D: Freme de-<br>skew &<br>parallize | 5000        | 5900        | realign independent bit-lanes    | Correlation Advanced                                                                          |

| E: Cmd check &<br>decode            | 3000        | 3000        | AMB specific                     | Buffer Data Logic R                                                                           |

| F: DRAM access                      | 25200       | 25200       | tRCD+tCAS+tDQSCK+CLK_Delay       |                                                                                               |

| G: Data<br>serialization            | 4500        | 4500        | includes CRC generation          |                                                                                               |

| H: Data merge<br>w/ NB traffic      | 1800        | 2800        | time to wait for frame alignment | Do sorialization<br>northboard 14 differential part bit laces from downlinem AMB              |

| I: NB<br>DIMM2DIMM<br>flight        | 600         | 900         | routing distance dependent       | Basis: 667 MT/s DDR2 Dram                                                                     |

| J: NB frame<br>resync               | 2000        | 3200        | may need to remerge on NB lanes  |                                                                                               |

| K: DIMM2CTLR<br>flight              | 800         | 1200        | routing distance dependent       | 2 AMB example – actual                                                                        |

| L: Frame-into-<br>CTLR              | 3000        | 3000        | deserialization delay            | latency increases w/ capacity                                                                 |

|                                     |             |             |                                  | e.g. # of FB-DIMMs<br>Typical – 1 <sup>st</sup> FB-Dimm operates<br>resync – rest in resample |