|     | Fix OOO Com                                        | oletion Prob             | lem First             |

|-----|----------------------------------------------------|--------------------------|-----------------------|

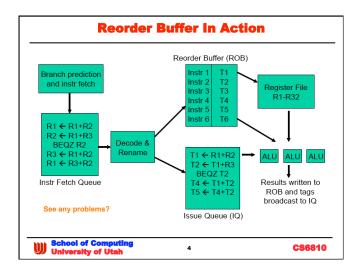

| •   | Enter the ROB (re-orde                             | r buffer)                |                       |

|     | <ul> <li>basic idea for now</li> </ul>             |                          |                       |

|     | » issue instructions in-                           | order                    |                       |

|     | » retire/commit instruc                            | tions in order           |                       |

|     | » use an intermediate i                            |                          | -                     |

|     | <ul> <li>since destructive ac<br/>order</li> </ul> | tion to register file or | memory must happen in |

| • ( | Other ROB niceties                                 |                          |                       |

|     | • helps w/                                         |                          |                       |

|     | » speculation                                      |                          |                       |

|     | » nullification                                    |                          |                       |

|     | » exceptions                                       |                          |                       |

|     | <ul> <li>but first a simple exan</li> </ul>        | nple                     |                       |

|     |                                                    |                          |                       |

|     |                                                    |                          |                       |

|     | School of Computing<br>University of Utah          | 3                        | C\$681(               |

| Nullification & Exceptions                                                                                                                                                                                                                                                                                                                                                                                                   | Decode Complexity                                                                                                                                    |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| If an exception happens<br>• exception type is written to the ROB field<br>» note that one instruction could generate an exception in<br>multiple stages<br>• only care about the first one so no overwrite is allowed<br>If some instruction is speculative<br>• then predicate is written to the ROB field<br>• note: predicate covers branch delay slots and effectively<br>supports nullification<br>WB stage in reality | ROB complicates ID significantly     operand fetch now has two sources                                                                               |  |  |

| try to retire a instructions per cycle     » if none have pending predicates or exceptions then retire     » in order retire → 1 <sup>st</sup> member of n-instruction bundle w/ problem     • retire the instructions before     • nullify whatever is next in the bundle     • take the exception and hold the rest                                                                                                        | ROB slots effectively provides a renamed register pool     actually it's not the right choice     Why?     remember the front-end back-end x86 thing |  |  |

| School of Computing<br>University of Utah 7 CS6810                                                                                                                                                                                                                                                                                                                                                                           | School of Computing<br>University of Utah a CS6810                                                                                                   |  |  |

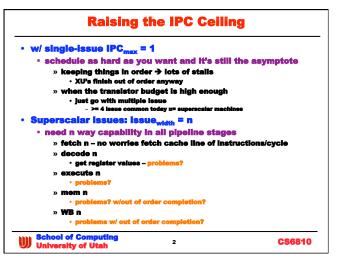

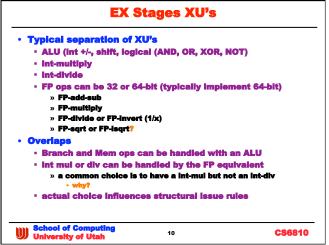

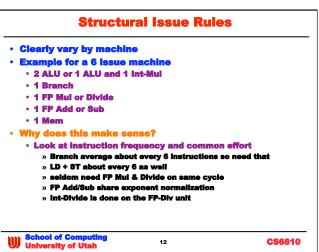

| <b>Structural Issue Rules</b>                 |         |       |

|-----------------------------------------------|---------|-------|

| Clearly vary by machine                       |         | · Cle |

| Example for a 6 issue machine                 |         | • Exa |

| • 2 ALU                                       |         |       |

| • 1 Branch                                    |         |       |

| <ul> <li>1 int Mui or Divide</li> </ul>       |         |       |

| <ul> <li>1 FP Add or Sub</li> </ul>           |         |       |

| • 1 Mem                                       |         |       |

| <ul> <li>Why does this make sense?</li> </ul> |         | • Wh  |

| • e.g. justification                          |         |       |

|                                               |         |       |

|                                               |         |       |

|                                               |         |       |

|                                               |         |       |

|                                               |         |       |

| School of Computing<br>University of Utah     | C\$6810 | W ur  |

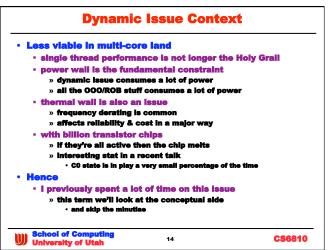

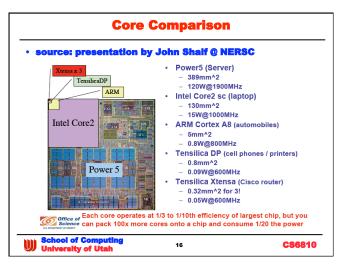

| : John             | Shalf            |                 |                         |

|--------------------|------------------|-----------------|-------------------------|

|                    | Traditional Core | Throughput Core |                         |

| uArch              | Out of Order     | In Order        |                         |

| Size               | 50               | 10              | mm^2                    |

| Power              | 37.5             | 6.25            | w                       |

| Freq               | 4                | 4               | GHz                     |

| Threads            | 2                | 4               |                         |

| Single<br>Thread   | 1                | 0.3             | Relative<br>Performance |

| Vector             | 4 (128-bit)      | 16 (512-bit)    |                         |

| Peak<br>Throughput | 32               | 128             | GFLOPS                  |

| Area<br>Capacity   | 0.6              | 13              | GFLOPS/mm               |

| Power<br>Capacity  | 0.9              | 20              | GFLOPS/W                |

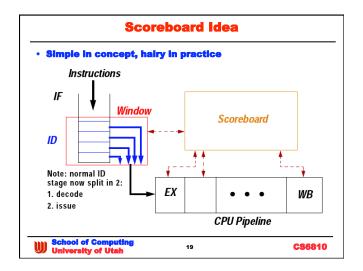

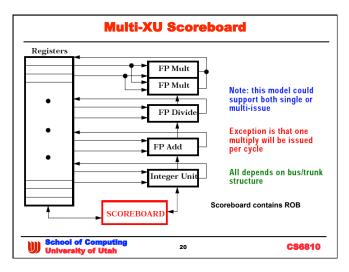

## **Not Shown**

- Memory ops

- scoreboard views memory interface as just another XU • Branches

- scoreboard tracks branch resolution

- » nullifies any speculative instructions in the branch delay slots

- Details of what the scoreboard entries contain

- similar to the ROB

- difference is centralized control

- » gets signals from everywhere and sends enables/selects back » round trip over long wires is prohibitive today for single core note it would work for small cores

but it consumes too much power

21

- » jury still out whether this is a dead tactic or not

School of Computing University of Utah

**CS6810**

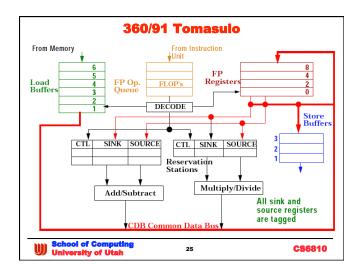

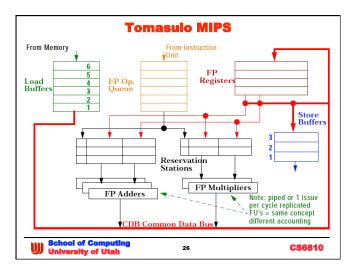

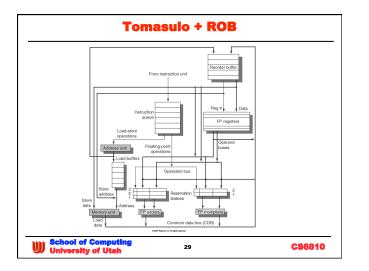

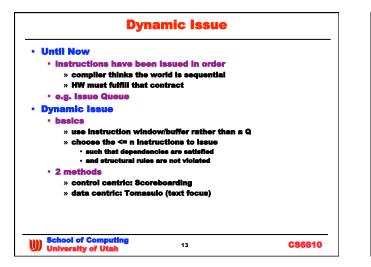

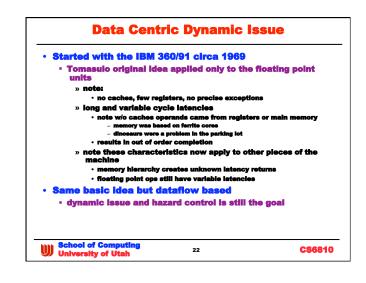

| <b>Different Control Model</b>                                             |                |                            |  |  |  |

|----------------------------------------------------------------------------|----------------|----------------------------|--|--|--|

| uitiple XU's                                                               |                |                            |  |  |  |

| fronted by <i>"reservation s</i>                                           | tations"       |                            |  |  |  |

| • when reservation station<br>instruction issues into ti                   | gets all of l  | it's operands the<br>ed XU |  |  |  |

| » out of order issue & out                                                 | of order com   | pletion                    |  |  |  |

| » basically a mechanism f<br>• which is the true seman                     |                | ting data-flow             |  |  |  |

| <ul> <li>XU's create results which<br/>reservation station slot</li> </ul> |                | i with the appropriate     |  |  |  |

| » equivalent of forwarding                                                 | y logic        |                            |  |  |  |

| Implicitly removes RAW                                                     |                | _                          |  |  |  |

| » values placed on a <i>"con</i>                                           |                |                            |  |  |  |

| <ul> <li>reservation station slots</li> <li>implicit renaming</li> </ul>   | s are register | 6                          |  |  |  |

| <ul> <li>Implicit renaming</li> <li>removes WAx hazard pi</li> </ul>       | roblem         |                            |  |  |  |

| eparate load and store (                                                   |                |                            |  |  |  |

| deals with the memory d                                                    | Ismbiguatio    | n Issue                    |  |  |  |

| » provides a write buffer (                                                | -              |                            |  |  |  |

| School of Computing<br>University of Utah                                  | 23             | C\$681                     |  |  |  |