|                        | to su                     | pport                | full forward                              | ling in the M                         | IPS                                                                     |

|------------------------|---------------------------|----------------------|-------------------------------------------|---------------------------------------|-------------------------------------------------------------------------|

| Source<br>Pipe<br>Reg. | Opcode of<br>Source Inst. | Dest.<br>Pipe<br>Reg | Opcode of<br>Dest. Inst.                  | Destination<br>of forwarded<br>result | Compare<br>if EQ then<br>forward                                        |

| EX/MEM                 | Reg-Reg ALU               | ID/EX                | Reg-Reg ALU<br>ALU-imm, LD,<br>ST, branch | Top ALU input                         | Rd(EX/MEM.IR <sub>16.20</sub> )<br>=<br>Rs1(ID/EX.IR <sub>6.,10</sub> ) |

| EX/MEM                 | Reg-Reg ALU               | ID/EX                | Reg-Reg ALU                               | Bottom ALU input                      | Rd(EX/MEM.IR <sub>1620</sub> )<br>=<br>Rs2(ID/EX.IR <sub>1115</sub> )   |

| MEM/WB                 | Reg-Reg ALU               | ID/EX                | Reg-Reg ALU<br>ALU-imm, LD,<br>ST, branch | Top ALU input                         | Rd(MEM/WB.IR <sub>1620</sub> )<br>=<br>Rs1(ID/EX.IR <sub>610</sub> )    |

| MEM/WB                 | Reg-Reg ALU               | ID/EX                | Reg-Reg ALU                               | Bottom ALU input                      | Rd(MEM/WB.IR <sub>1620</sub> )<br>=<br>Rs2(ID/EX.IR <sub>610</sub> )    |

| Source<br>Pipe<br>Reg. | Opcode of<br>Source Inst. | Dest.<br>Pipe<br>Reg | Opcode of<br>Dest. Inst.                  | Destination<br>of forwarded<br>result | Compare<br>if EQ then<br>forward                                      |

|------------------------|---------------------------|----------------------|-------------------------------------------|---------------------------------------|-----------------------------------------------------------------------|

| EX/MEM                 | ALU Immediate             | ID/EX                | Reg-Reg ALU<br>ALU-imm, LD,<br>ST, branch | Top ALU input                         | Rd(EX/MEM.IR <sub>1115</sub> )<br>=<br>Rs1(ID/EX.IR <sub>610</sub> )  |

| EX/MEM                 | ALU Immediate             | ID/EX                | Reg-Reg ALU                               | Bottom ALU input                      | Rd(EX/MEM.IR <sub>1115</sub> )<br>=<br>Rs2(ID/EX.IR <sub>1115</sub> ) |

| MEM/WB                 | ALU Immediate             | ID/EX                | Reg-Reg ALU<br>ALU-imm, LD,<br>ST, branch | Top ALU input                         | Rd(MEM/WB.IR <sub>1115</sub> )<br>=<br>Rs1(ID/EX.IR <sub>610</sub> )  |

| MEM/WB                 | ALU Immediate             | ID/EX                | Reg-Reg ALU                               | Bottom ALU input                      | Rd(MEM/WB.IR <sub>1115</sub> )<br>=<br>Rs2(ID/EX.IR <sub>1115</sub> ) |

| Source       | Opcode of    | Dest.       | Opcode of                                 | Destination            | Compare                                                               |

|--------------|--------------|-------------|-------------------------------------------|------------------------|-----------------------------------------------------------------------|

| Pipe<br>Reg. | Source Inst. | Pipe<br>Reg | Dest. Inst.                               | of forwarded<br>result | if EQ then<br>forward                                                 |

| MEM/WB       | Load         | ID/EX       | Reg-Reg ALU<br>ALU-imm, LD,<br>ST, branch | Top ALU input          | Rd(MEM/WB.IR <sub>1115</sub> )<br>=<br>Rs1(ID/EX.IR <sub>610</sub> )  |

| MEM/WB       | Load         | ID/EX       | Reg-Reg ALU                               | Bottom ALU input       | Rd(MEM/WB.IR <sub>1115</sub> )<br>=<br>Rs2(1D/EX.IR <sub>1115</sub> ) |

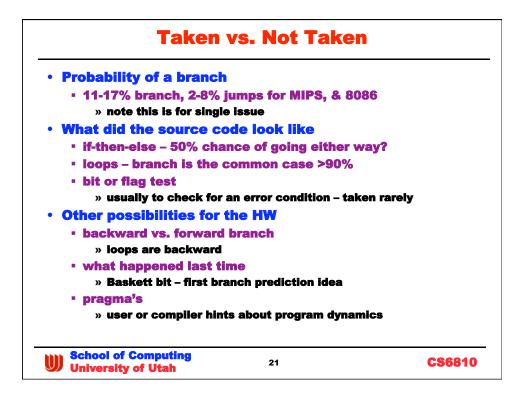

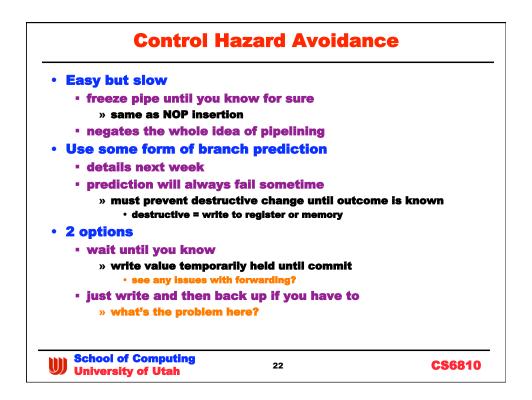

| <b>Control Hazards</b>                      |                      |                      |  |  |

|---------------------------------------------|----------------------|----------------------|--|--|

| • More evil than data ha                    | zards                |                      |  |  |

| <ul> <li>since forwarding does</li> </ul>   | sn't help            |                      |  |  |

| • Need 3 things – 2 happ                    | pen late in the pip  | beline               |  |  |

| <ul> <li>branch target</li> </ul>           |                      |                      |  |  |

| » PC+4 if branch not t                      | aken or address (con | nputed or immediate) |  |  |

| <ul> <li>condition true?</li> </ul>         |                      |                      |  |  |

| » output of zero unit i                     |                      |                      |  |  |

| » condition code, ir                        |                      |                      |  |  |

| <ul> <li>decode stage recogni</li> </ul>    | izes a branch or jur | np                   |  |  |

| • Result                                    |                      |                      |  |  |

| <ul> <li>IF of wrong instruction</li> </ul> | -                    |                      |  |  |

| Simple MIPS pipeline I                      | has 3 cycle brand    | h delay penalty      |  |  |

| <ul> <li>effective address not</li> </ul>   | known until EX       |                      |  |  |

| <ul> <li>condition set in MEM</li> </ul>    | (stage 4)            |                      |  |  |

| » 3 branch delay slots                      | 5                    |                      |  |  |

| School of Computing<br>University of Utah   | 18                   | CS6810               |  |  |

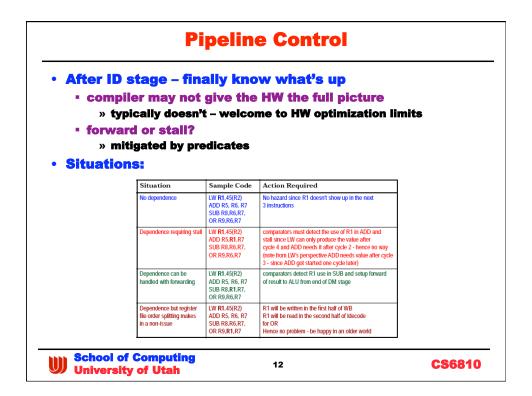

|          | act to IPC/     | CPI is<br>w/ brai | 2-17% of<br>nch penal |         |

|----------|-----------------|-------------------|-----------------------|---------|

| Code     | Total<br>Wasted | Empty<br>Slots    | Cancelled             |         |

| compress | 30%             | 18%               | 12%                   |         |

| eqntott  | 35%             | 24%               | 11%                   |         |

| espresso | 34%             | 30%               | 4%                    | SPECint |

| gcc      | 26%             | 15%               | 11%                   | or Lonn |

| li       | 46%             | <b>19%</b>        | 27%                   |         |

| doduc    | 40%             | 34%               | 6%                    |         |

| ear      | 41%             | 37%               | 4%                    |         |

| hydro2d  | 16%             | 1%                | 15%                   | SPECfp  |

| mdljdp   | 8%              | 1%                | 7%                    |         |

| su2cor   | 17%             | 7%                | 10%                   |         |

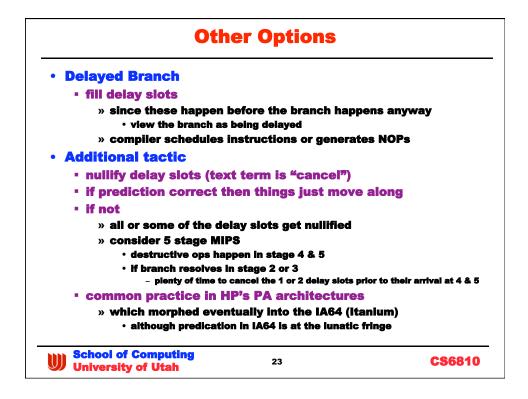

| ideal CPI=1 a<br>te penalty = 3 i |                            | _                          |                                                         | -                                                                   | ame |

|-----------------------------------|----------------------------|----------------------------|---------------------------------------------------------|---------------------------------------------------------------------|-----|

| Pipeline Spe                      | edup = $\frac{1}{1 + B_1}$ | Pipeline<br>ranch Frequenc | e Depth<br>cy × Branch Pe                               | malty                                                               |     |

| Scheduling<br>Scheme              | Branch<br>Penalty          | Effective<br>CPI           | Pipeline<br>Speedup<br>over<br>Non-<br>piped<br>Version | Pipeline<br>Speedup<br>over<br>Stall Pipe<br>on<br>Branch<br>Scheme |     |

| Stall pipeline                    | 3                          | 1.42                       | 3.5                                                     | 1.0                                                                 | 1   |

| Predict Taken                     | 1                          | 1.14                       | 4.4                                                     | 1.26                                                                | 1   |

| Predict Not Taken                 | 1                          | 1.09                       | 4.5                                                     | 1.29                                                                | 1   |

| Delayed Branch                    | 0.5                        | 1.07                       | 4.6                                                     | 1.31                                                                | 1   |

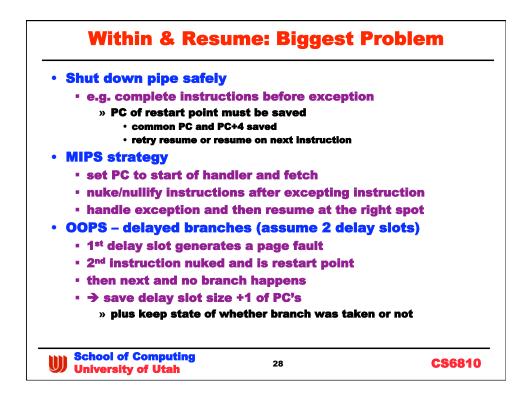

| <b>5 Axis Exception Model</b>        |                                                  |               |  |  |

|--------------------------------------|--------------------------------------------------|---------------|--|--|

| • Sync vs. Async                     | C                                                |               |  |  |

| synch – asso                         | ciated with a particular instr                   | uction        |  |  |

| » handler re                         | places instruction and then retri                | es or aborts  |  |  |

|                                      | truction independent (e.g. OS<br>and then handle | timeout)      |  |  |

| » power fail                         | : may not have time to do a com                  | olete flush   |  |  |

| Code requeste                        | d vs. coerced                                    |               |  |  |

| <ul> <li>req'd is pred</li> </ul>    | ictable and can happen after                     | instruction   |  |  |

| • Maskable or n                      | ot                                               |               |  |  |

| <ul> <li>arith. overflo</li> </ul>   | w: the code can care or not                      |               |  |  |

| • Within vs. betv                    | ween instructions                                |               |  |  |

| <ul> <li>similar to syn</li> </ul>   | nc/async w/ small difference                     |               |  |  |

|                                      | rminate program                                  |               |  |  |

| <ul> <li>handle and read</li> </ul>  |                                                  |               |  |  |

|                                      | on just terminates (e.g. segm                    | ent error)    |  |  |

| School of Compu<br>University of Uta |                                                  | <b>CS6810</b> |  |  |

|                           |             | •              |              |          |                 |

|---------------------------|-------------|----------------|--------------|----------|-----------------|

| Exc. Type                 | Synchronous | Requested -    | mask -       | within - | resume -        |

|                           | - Asynch.   | Coerced        | non-mask     | between  | terminate       |

| I/O Device Req.           | Asynch      | Coerced        | Non-maskable | Between  | Resume          |

| Invoke OS svc.            | Synch       | User Requested | Non-maskable | Between  | Resume          |

| Trace/Bkpoint             | Synch       | User Requested | Maskable     | Between  | Resume          |

| Arith. exception          | Synch.      | Coerced        | Maskable     | Within   | Resume          |

| Page Fault                | Synch.      | Coerced        | Non-maskable | Within   | Resume          |

| Misaligned addr.          | Synch       | Coerced        | Maskable     | Within   | Resume          |

| Mem. prot. viola-<br>tion | Synch       | Coerced        | Non-maskable | Within   | Resume          |

| Undefined Inst.           | Synch.      | Coerced - ???  | Non-maskable | Within   | Terminate - ??? |

| HW error                  | Asynch.     | Coerced        | Non-maskable | Within   | Terminate       |

| Power Failure             | Asynch      | Coerced        | Non-maskable | Within   | Terminate       |

|                           |             |                |              |          |                 |

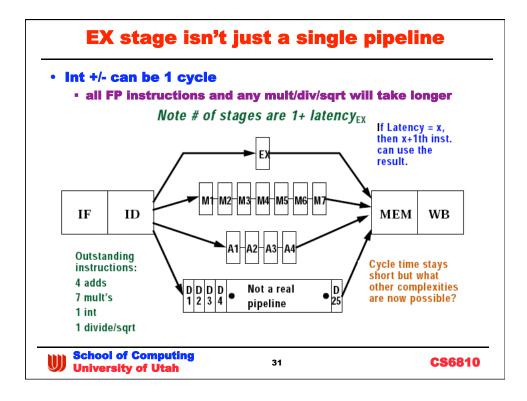

|       | Latenoy                                    | & Repeat                          |                                    |

|-------|--------------------------------------------|-----------------------------------|------------------------------------|

| • Lat | ency – number of                           | f cycles to gen                   | erate value                        |

| • •   | w/ forwarding defin<br>intervening instruc |                                   | to be the number of                |

|       | hence 0 means ne>                          | ct instruction ca                 | n consume the result               |

| • Rej | peat/Initiation int                        | erval                             |                                    |

|       | instruction                                | 4                                 |                                    |

| • Exa | » defined in cycles<br>ample<br>XU         | -                                 | Initiation Interval                |

| • Exa | ample                                      | - 1 means next cy<br>Latency<br>0 |                                    |

| • Exa | xu                                         | Latency                           | Initiation Interval                |

| • Exa | XU<br>Inteter ALU                          | Latency<br>0                      | Initiation Interval                |

| • Exa | XU<br>Inteter ALU<br>Loads                 | Latency<br>0<br>1                 | Initiation Interval11              |

| • Exa | XU<br>Inteter ALU<br>Loads<br>FP +/-       | Latency<br>0<br>1<br>3            | Initiation Interval<br>1<br>1<br>1 |

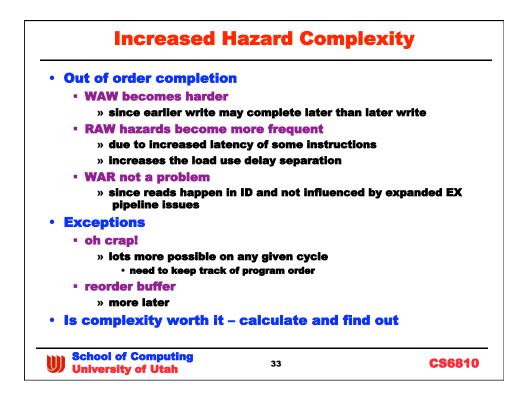

| Things you can do wrong                            |                                                                                                       |                |  |  |  |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------|--|--|--|

| • Sophisticated add                                | ress modes                                                                                            |                |  |  |  |

| required → more<br>» fill and spill to r           | during EFA calculation<br>registers or higher regi<br>memory is expensive in tim<br>ment or decrement | ister pressure |  |  |  |

| Permit self-modify                                 | ing code (ala 80x86)                                                                                  |                |  |  |  |

|                                                    | ruction in the pipeline<br>restart a different instruct                                               | lon            |  |  |  |

| Implicitly set cond                                | ition codes                                                                                           |                |  |  |  |

| <ul> <li>later instruction s</li> </ul>            |                                                                                                       |                |  |  |  |

| <ul> <li>earlier but finishe</li> </ul>            | s later instruction sets                                                                              | code           |  |  |  |

| <ul> <li>branch comes ald</li> <li>fix?</li> </ul> | ong and uses the stale o                                                                              | condition      |  |  |  |

| School of Computing<br>University of Utah          | 34                                                                                                    | <b>CS6810</b>  |  |  |  |

|     | Take Home Wisdom                                                                             |                                   |                |  |  |

|-----|----------------------------------------------------------------------------------------------|-----------------------------------|----------------|--|--|

| •   | Pipelining                                                                                   |                                   |                |  |  |

|     | <ul> <li>simple concept – arbitraria</li> </ul>                                              | itrarily hard to get rig          | ght in reality |  |  |

| • • | Things will get even h                                                                       | arder                             |                |  |  |

|     | • superscalar – multipl                                                                      |                                   |                |  |  |

|     | • deeper pipelines to i                                                                      | ncrease frequency                 |                |  |  |

|     | » laminarity and stall                                                                       | probability problems in           | crease         |  |  |

|     | <ul> <li>compiler instruction</li> </ul>                                                     | scheduling gets trick             | <b>cier</b>    |  |  |

|     | » can the hardware n <ul> <li>yes but it's compil</li> </ul>                                 | nake up some of the sla<br>Icated | ck?            |  |  |

| •   | Late 80's                                                                                    |                                   |                |  |  |

|     | <ul> <li>improved performance</li> </ul>                                                     | e ran out of gas                  |                |  |  |

|     | <ul> <li>multiple issue saves</li> </ul>                                                     | the 90's (ILP)                    |                |  |  |

|     | <ul> <li>multiple cores saves</li> </ul>                                                     | the next decade - T               | BD?            |  |  |

|     | <ul> <li>TLP affects the prop<br/>pipelining and ILP d</li> <li>for the most part</li> </ul> | -                                 |                |  |  |

| W   | School of Computing<br>University of Utah                                                    | 36                                | <b>CS6810</b>  |  |  |