# **Solid State NVRAM Technologies**

### **Today's topics:**

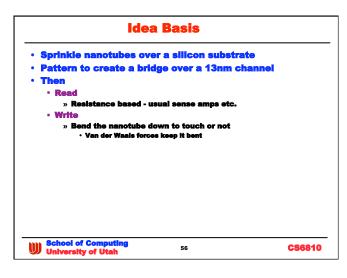

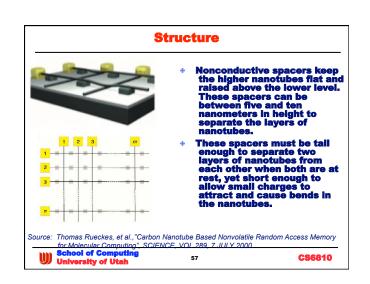

Flash, PCRAM, SONOS, FeRAM, MRAM, Probe Storage, NRAM, RRAM

basically a survey of current (FLASH) and future technologies - they will be disruptive if they succeed

School of Computing University of Utah

CS6810

# **Generic Taxonomy: V & NV**

- Volatile

- SRAM 5 or 6 transistors per cell

- » fast but costly & power hungry

- » usage

- on chip caches, register files, buffers, queues, etc.

off chip usage now rare except in embedded space

DRAM 1 T & 1 C per cell (lots of details later in the term)

» focus on density and cost/bit

- too bad both power and delay properties are proble

- usage main memory

EDRAM now moving on chip for large "last cache" duti

- » specialty parts for mobile systems

- · low-power · self-refresh

- takes advantage of light usage

battery backed DRAM common in data-center

School of Computing University of Utah

CS6810

# NV

- Traditional non-volatile

- Magnetic Disk

- » cheap

- » mbxed use: file system and scratch

- · CD, DVD

- » even cheaper per unit but less capacity » media and SW distribution, personal archival

- - » cheapest

- » archival storage

- Solid state

- » more spendy but faster

- PROM in various flavors now primarily masked on chip

FLASH has essentially taken over at the component level

new contenders are on the horizon however

3

School of Computing University of Utah

CS6810

# **Some Observations**

- Bandwidth and Latency

- both are important

- » latency problems can be hidden to some extent » bandwidth problems are much harder to hide

- · Increasing the storage hierarchy depth

- conventional approach

» big memories are slow

- » helps with fragmentation & BW issues

- · Yale vs. Harvard - conflicts with power constraints now

- » moving lots of bits over long wires is energy expensive

- Somewhat troubling

- how little mem\_arch has changed in 60 years

- opportunity

School of Computing University of Utah

CS6810

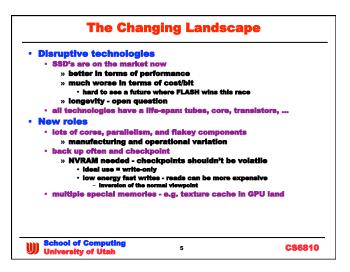

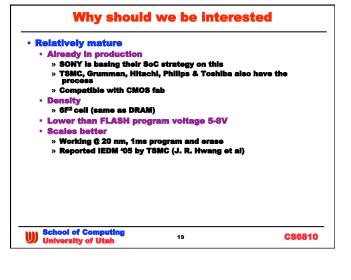

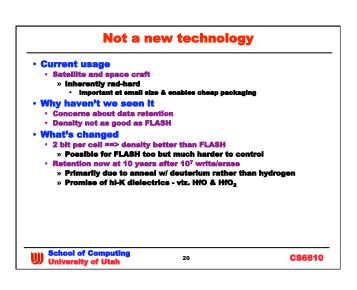

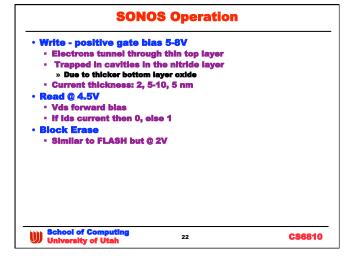

# What's Wrong with FLASH?

# No problem unless

- You care about speed, power

» Looks good when compared to disk except for price

OR operate in write rarely land

- There are some alternatives BUT

- They all have some downs

- » Maturity, expense, density, market & investment, etc.

- » Scaling claims just how real are they

- Worth tracking since FLASH futures may not be bright

- · IEDM 2005 Panel ==> run out of gas in 2010 likely?

- Vendors disagree of course

- Question

- obvious market niche: thumb drives, cameras, etc.

SSD and checkpoint storage role might be in doubt

School of Computing University of Utah

CS6810

# **What's Next?**

- Talk about likely future NVRAM candidates

- Ignore quantum and DNA soup like structure

- » Distant future maybe near future unlikely

- » Note: fab ramp is as important as the devices

- Many have been around for a long t

- » Development to deployment is a long and rocky road

- How they work focus

- Maybe more technology than a user cares about

- Hopefully ald awareness of what to look for as the technologies progress

Architects must track technology trends

- Try and assess where their future might lie

Memory shapes the systems around it

» A fact most architects have ignored to date

- - » Von Neumann's corollary

School of Computing University of Utah

CS6810

# Flash (Hot Chips '04)

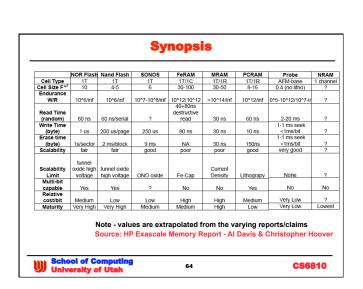

|                      | -                      | -                 |

|----------------------|------------------------|-------------------|

|                      | NOR Flash              | NAND Flash        |

| Applications         | Code, data             | Mass storage      |

| Future applications  | MLC: mass storage      | Code and data     |

| Density range        | Up to 512Kb            | Up to 4Gb         |

| READ latency         | 60ns-120ns             | 25µs              |

| Max Read bandwidth   | 41 MB/s-112 MB/s (16b) | 40 MB/s (16b bus) |

| Max Write bandwidth  | 0.25 MB/s              | 5MB/s             |

| Erase time           | 400ms (128KB blk)      | 2ms (128KB block) |

| Read device current  | 1.6x                   | 1x                |

| Write device current | 3x                     | 1x                |

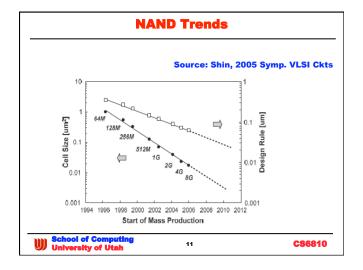

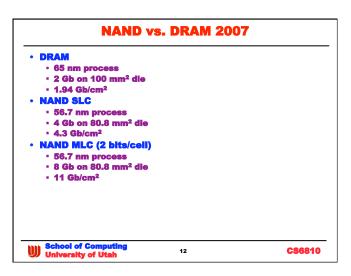

Note - NAND read times haven't changed in years

Density improvement is excellent

School of Computing University of Utah

CS6810

# **Known FLASH issues**

- Speed slow writes OK, but 25 usec reads??

- High voltage on both read and write create problems

Charge pump takes time

- » Jitter on bit lines requires lengthy settle margin

- · Conclusion is that reads are unlikely to get much faste

- - · Thicker tunnel oxide (7-12nm) provides good retention, but

- High voltage requirements create reliability issue.

Channel punch through, junction breakdown, etc.

Also increases the read and write energies

- Scaling

- Concern over single defect memory loss limits vertical scaling

- · High voltage also limits lateral scaling to some extent

- Rad hard arrays are difficult to achieve

- · Support circuitry doesn't scale as well as the arrays

School of Computing University of Utah

16

CS6810

#

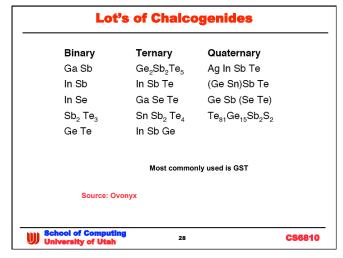

# **Basically a very cheap material**

### Cost/Bit Reduction

- Small active storage medium

- Small cell size small die size

- Simple manufacturing process low step count

- Simple planar device structure

- Low voltage single supply

- Reduced assembly and test costs

Source: Ovonyx

CS6810

# **Ovonyx claimed advantages**

# **Near-Ideal Memory Qualities**

- Non-volatile

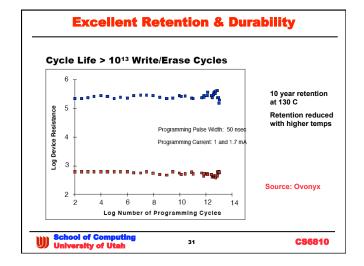

- High endurance ->1013 demonstrated

- Long data retention ->10 years

- Static no refresh overhead penalty

- Random accessible read and write

- High switching speed

- Non-destructive read

- Direct overwrite capability

- Low standby current (<1µA)

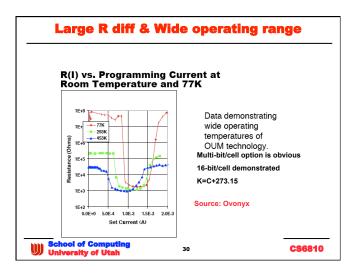

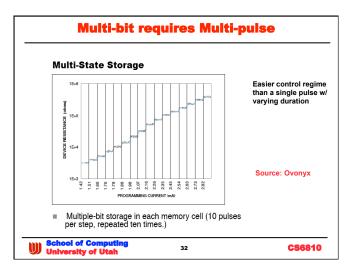

- Large dynamic range for data (>40X)

- Actively driven digit-line during read

- Good array efficiency expected

- No memory SER RAD hard

- No charge loss failure mechanisms

CS6810

# **Other Advantages**

- Scalability

- · Primarily limited by lithography

- » Caveat thermal isolation bands may not scale as well

- Claim is quaternary materials are the solution here

Performance improves linearly w/ feature size

- · What we care about in a read mostly environment

- » Where the ideal is read never since nothing bad happened

- Read time is short

- · Low read energy

- 3D possible w/ epitaxial thin films

- · Claimed but not demonstrated as far as I can tell

35

CS6810

# OK where's the downside

- Based on the Ovonyx spin

Everybody should use this stuff and FLASH should be dead

- · HEAT

- ctors give off ~50% of their power as heat

- » The rest is returned to the power supply

- in write operations ~100% of the power is given off as heat

Longer quench time if writes to same neighborhood control problem

- Issues

Retention tracks ambient temps

Good cooling means higher write currents

BIG ONE: material defect issues currently have yield issues

» It's a long way from the lab to profitable product

36

CS6810

CS6810

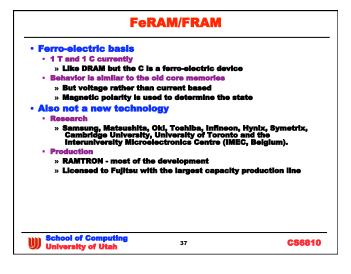

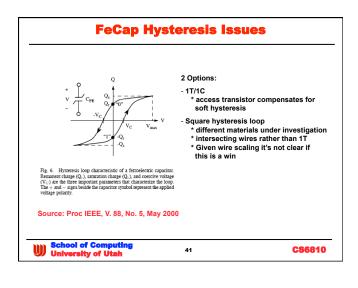

### Compared w/ Flash and EEPROM Nonvolatile Memory Write (prog.) Access-Time Area/Cell Read Energy\* per 32b Write Access-Time (normalized) EEPROM 2 50ns 10μs 1μJ 150pJ Flash Memory 100ns 150pJ 50ns $2\mu J$ Ferroelectric Memory 5 (†) 100ns 100ns 1nJ lnJ Note: Flash access times are not correct - makes one wonder about the rest -- the stacked version area is 2x bigger than Flash -- Larger size is due to old process \* 2005 Fujitsu line used 350 nm for FeRAM \* 2006 Toshiba Flash process in 60 nm -- Scalability of the Fe Cap is not discussed Source: Proc IEEE, V. 88, No. 5, May 2000 School of Computir University of Utah CS6810 40

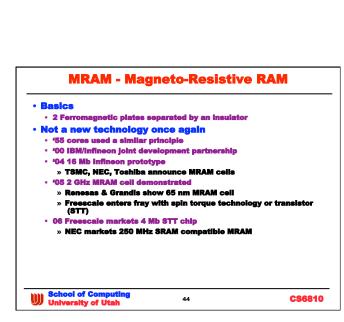

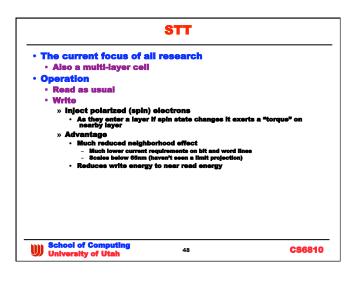

# Properties Power Read energy =~ DRAM but w/ no refresh Stain 99% less in normal operation Write energy 3-8x > DRAM for classic STT solves this as Rd and Wr energy ~ same Longevity Indefinite Density Until market adopts non-critical (a.k.a. large) fabs used B\$+ fab is the key barrier Hence nowhere near DRAM or FLASH in maturity