# DRAM Today's topics: Brief look at DRAM devices Channel protocols & signalling Memory controller issues This is just a skim – CS7810 will have a more in depth treatment of lots of topics including this one

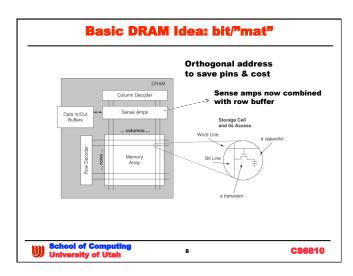

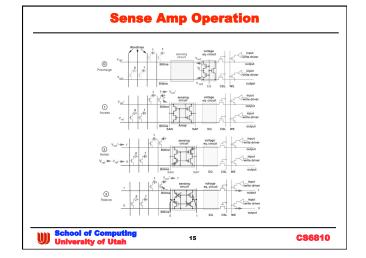

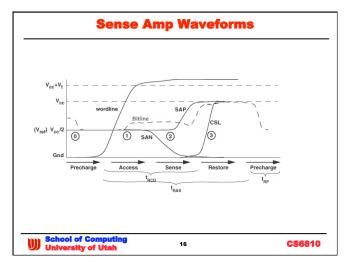

## Sense Amps • Small stored charge requires high sensitive amps • use differential model » reference voltage precharged to half-way mark » then look at which way the charge goes to determine value • noise margins must exist and trick is to keep them small • problematic as devices shrink • Roles • 1: basic sense value • 2: restore due to the destructive read » 2 variants in play • restore instantly or restore on row close • 3: act as a temporary storage element (row buffer) » how temporary depends on restore choice

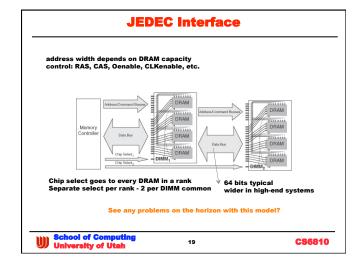

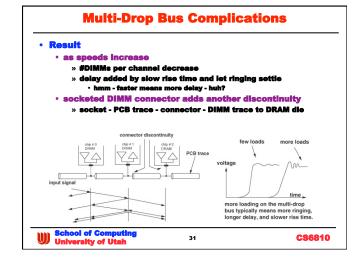

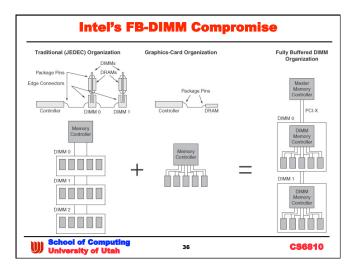

## Disturbing Trend Disturbing Trend DIMM capacity going up process improvements yield more bits/die DRAM channel speed going up DRAM channel speed going DOWNII SDR - 8 DIMMs/channel DDR - 4 DIMMs/channel DDR - 4 DIMMs/channel DDR - 1 DIMM/channel DDR - 1 DIMM/channel DDR - 1 DIMM/channel DDR - 2 DIMMs/channel Nember bound? Setup did the set of the set of the did the set of the set of the did the set of the set of the did the set of the s

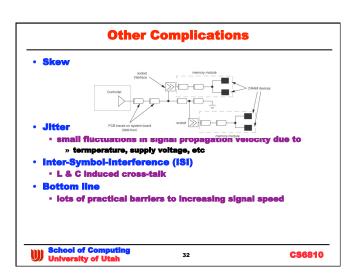

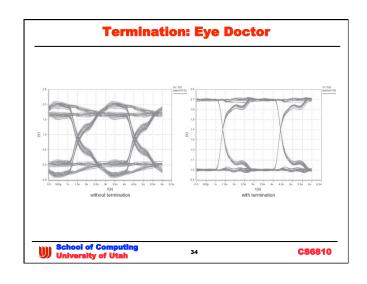

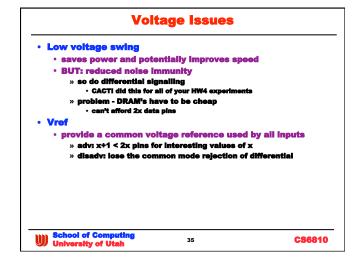

## Key to minimizing reflections but DRAM needs to be cheap being SQJ and TSOP packages iarge pin C & L's - mismatched to trace impedance Of for low freq -< 200 litiz faster requires smaller pins ==> BGA (DDR) & FBGA (DDR2/3) Another termination issue impedance inside vs. outside the package need to be isolated series termination (DDR) demps internal DRAM component reflection effects on the DIMM trace programmable on die parallel termination (DDR2) inligher speeds ==> tighter reflection constraints configuration register controls termination resistor switches removes need to time for worst case configurations (max DIMMs) School of Computing University of Utah

CS6810

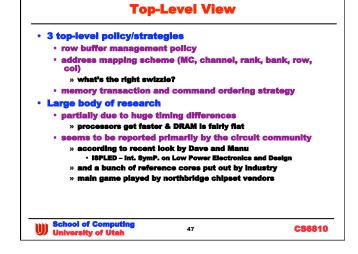

### **Row Buffer Management**

- Open-Page

- good

- » both temporal and spatial locality exist in access pattern

- spatial: amortizes large row activate energy cost

temporal: energy to keep row open results in improved ba

latency limited by t<sub>oss</sub> only

- - » energy: active row but no accesses

- » time: precharge, activate, access if target row is inactive

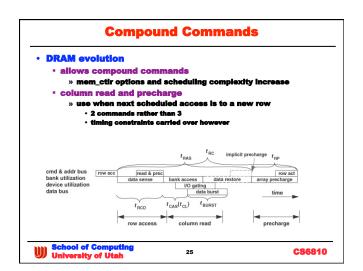

better to perform a col-rd-precharge command when new row is

known

- scheduling issues

- » similar to dynamic instruction issue

- imitar to dynamic instruction issue

performance increases with a larger window

except when window is always slightly filled

multi-core/life changes the probability

dependent and anti-dependent issues must be tracked

note write buffer in XDR (sound familiar?)

CS6810

### **Concluding Remarks**

- Whiriwind tour phew!

- Take homes

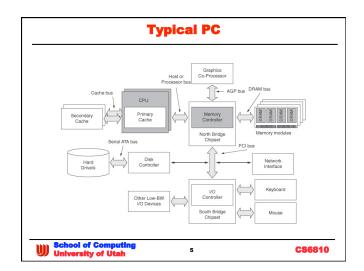

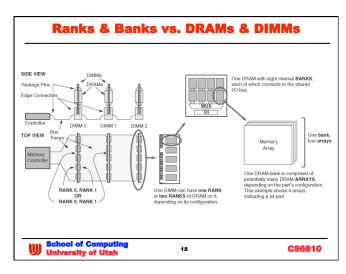

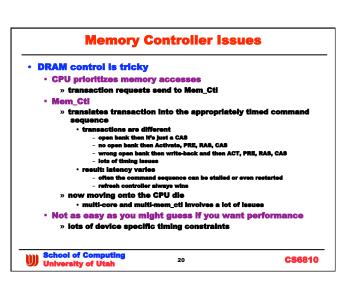

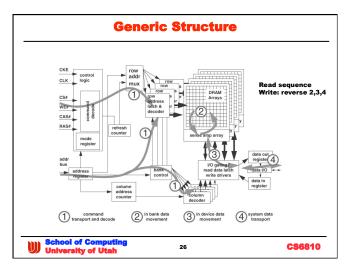

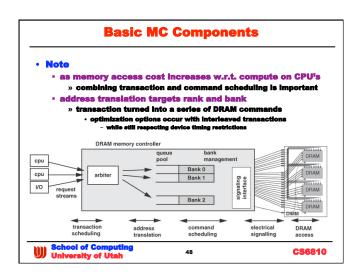

- · understand role of MC, channel, rank, bank, row & column

- · large mat delay & broadcast commands

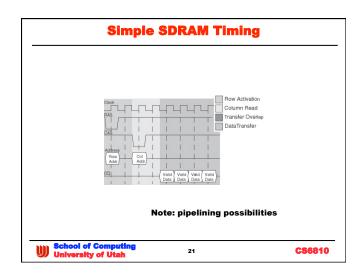

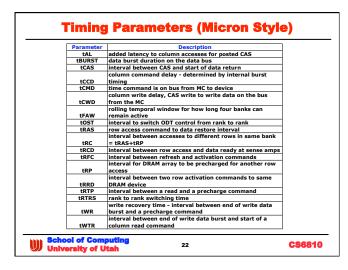

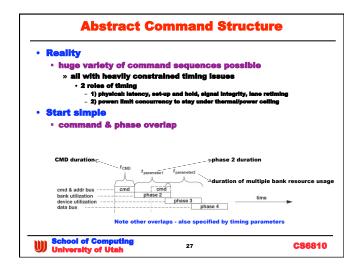

- » MC role is to overlap commands optimally

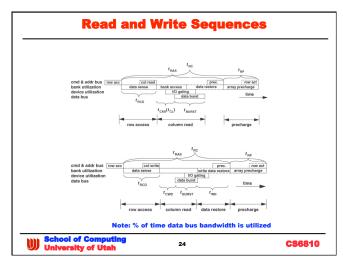

- » best bandwidth -> keep data bus active

- » open and closed row scheduling policy idea

- · challenges for the future

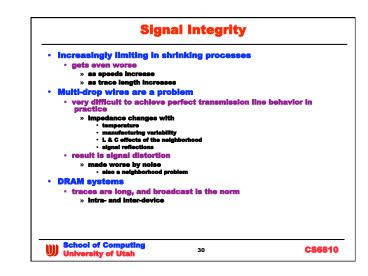

- » signal integrity limits bus speed

- » cpu pin count limits channel width

- Multi-core and improved process technology

- only makes things worse

- more compute power → higher memory pressure

- » caches help and are critical

- » but they can't catch everything

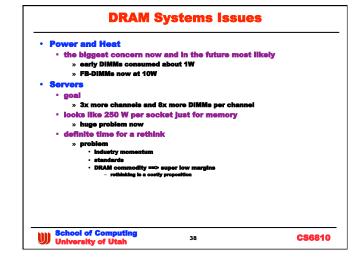

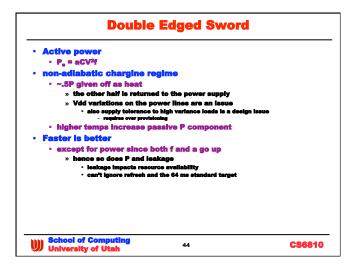

- power is and will continue to be a fundamental constraint

CS6810