| Plan Preview                                       |                                                                  |               |  |  |  |  |

|----------------------------------------------------|------------------------------------------------------------------|---------------|--|--|--|--|

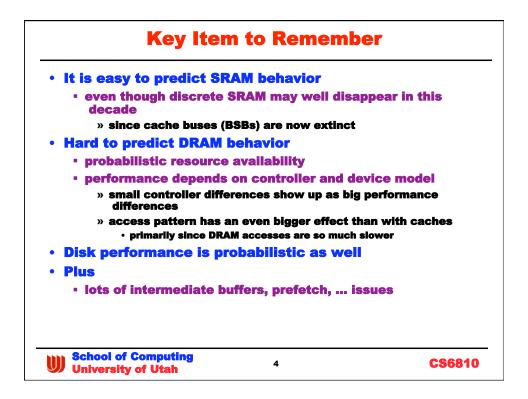

| • So far focus has bee                             | n on-chip                                                        |               |  |  |  |  |

| <ul> <li>processors, caches</li> </ul>             |                                                                  |               |  |  |  |  |

| • and a bit of intercor                            | inect                                                            |               |  |  |  |  |

| <ul> <li>brief look at paralle</li> </ul>          | l processing on 1 or mor                                         | e sockets     |  |  |  |  |

| <ul> <li>Note that many big a<br/>bound</li> </ul> | pplications are I/O or                                           | memory        |  |  |  |  |

| Iast 3 lectures before                             | re the 2 <sup>nd</sup> midterm                                   |               |  |  |  |  |

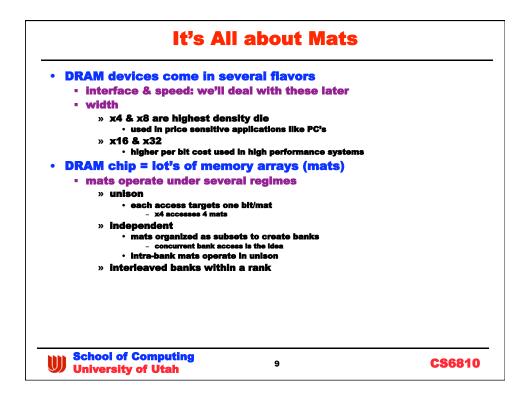

| » DRAM – this one                                  |                                                                  |               |  |  |  |  |

| • 2 standards                                      |                                                                  |               |  |  |  |  |

|                                                    | ) — focus on this one — 64 bit slower (<br>RAM — fast skinny bus | data bus      |  |  |  |  |

| <ul> <li>pace will be rapid</li> </ul>             | d – high level understanding is                                  | the goal      |  |  |  |  |

| » Disk and storage                                 |                                                                  |               |  |  |  |  |

| » non-volatile RAM (                               | e.g. not disk)                                                   |               |  |  |  |  |

| • goal is to give you a                            | high level understandin                                          | )g            |  |  |  |  |

| » details are way to                               | o complicated to cover in 1                                      | .5 weeks      |  |  |  |  |

|                                                    |                                                                  |               |  |  |  |  |

| School of Computing<br>University of Utah          | 2                                                                | <b>CS6810</b> |  |  |  |  |

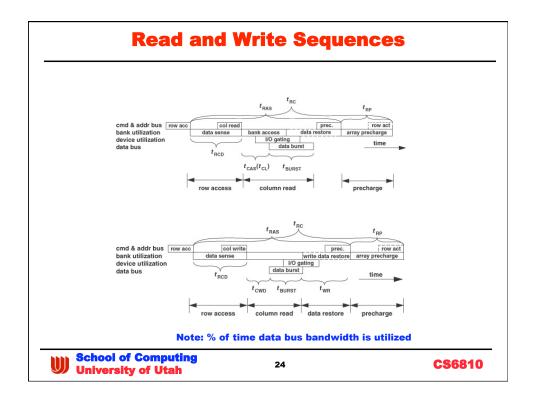

| P | arameter | Description                                              |  |

|---|----------|----------------------------------------------------------|--|

|   | tAL      | added latency to column accesses for posted CAS          |  |

|   | tBURST   | data burst duration on the data bus                      |  |

|   | tCAS     | interval between CAS and start of data return            |  |

|   |          | column command delay - determined by internal burst      |  |

|   | tCCD     | timing                                                   |  |

|   | tCMD     | time command is on bus from MC to device                 |  |

|   |          | column write delay, CAS write to write data on the bus   |  |

|   | tCWD     | from the MC                                              |  |

|   |          | rolling temporal window for how long four banks can      |  |

|   | tFAW     | remain active                                            |  |

|   | tOST     | interval to switch ODT control from rank to rank         |  |

|   | tRAS     | row access command to data restore interval              |  |

|   |          | interval between accesses to different rows in same bank |  |

|   | tRC      | = tRAS+tRP                                               |  |

|   | tRCD     | interval between row access and data ready at sense amps |  |

|   | tRFC     | interval between refresh and activation commands         |  |

|   |          | interval for DRAM array to be precharged for another row |  |

|   | tRP      | access                                                   |  |

|   |          | interval between two row activation commands to same     |  |

|   | tRRD     | DRAM device                                              |  |

|   | tRTP     | interval between a read and a precharge command          |  |

|   | tRTRS    | rank to rank switching time                              |  |

|   |          | write recovery time - interval between end of write data |  |

|   | tWR      | burst and a precharge command                            |  |

|   |          | interval between end of write data burst and start of a  |  |

|   | tWTR     | column read command                                      |  |

|                       | MI   |           | na     | al     | TIM                                | ing Equations                         |        |

|-----------------------|------|-----------|--------|--------|------------------------------------|---------------------------------------|--------|

| A=row access          | _    |           |        | _      |                                    |                                       |        |

| R=col rd              |      | Next<br>A |        |        | Min. Timing<br>tRC                 | Notes                                 |        |

|                       | A    | A         | s<br>s | s<br>d | tRC                                | plus tFAW for 5th RAS same rank       |        |

| W=col_wr              | P    | Ä         | s      | d      | tRP                                | plus traw for 5th kas same rank       |        |

| P=precharge           | Ē    | Â         | s      | s      | tRFC                               |                                       |        |

| F=Refresh             | Α    | R         | s      | s      | tRCD-tAL<br>Max(tBURS              | tAL=0 unless posted CAS               |        |

| s=same<br>d=different | R    | R         | s      | а      | T, tCCD)<br>tBURST+                | tBURST of previous CAS, same rank     |        |

| a=any                 | R    | R         | d      | а      | tRTRS<br>tCWD+<br>tBURST+          | tBURST prev. CAS diff. rank           |        |

|                       | w    | R         | s      | а      | tWTR<br>tCWD+tBU<br>RST+tRTRS      | tBURST prev CASW same rank            |        |

|                       | w    | R         | d      | а      | tCAS                               | tBURST prev CASW diff rank            |        |

|                       | Α    | w         | s      | s      | tRCD-tAL<br>tCAS+tBUR              |                                       |        |

|                       | R    | w         | а      | а      | ST+tRTRS-<br>tCWD<br>Max(tBURS     | tBURST prev. CAS any rank             |        |

|                       | w    | w         | s      | а      | T, tCCD)<br>tBURST+tO              | tBURST prev CASW same rank            |        |

|                       | w    | w         | d      | а      | ST                                 | tBURST prev CASW diff rank            |        |

|                       | A    | Р         | s      | s      | tRAS<br>tAL+tBURS<br>T+ tRTP-      |                                       |        |

|                       | R    | Ρ         | S      | S      | tCCD<br>tAL+tCWD<br>+<br>tBURST+tW | tBURST of previous CAS, same rank     |        |

|                       | w    | Р         | s      | s      | R                                  | tBURST prev CASW same rank            |        |

|                       | F    | F         | s      | a      | tRFC                               | · · · · · · · · · · · · · · · · · · · |        |

|                       | Р    | F         | s      | а      | tRFC                               |                                       |        |

| Universit             | Comp | outi      | ng     |        |                                    | 23                                    | CS6810 |

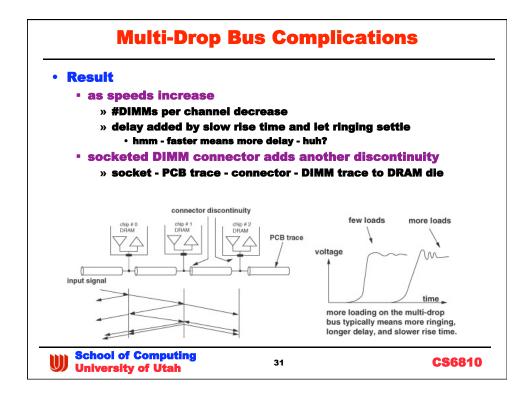

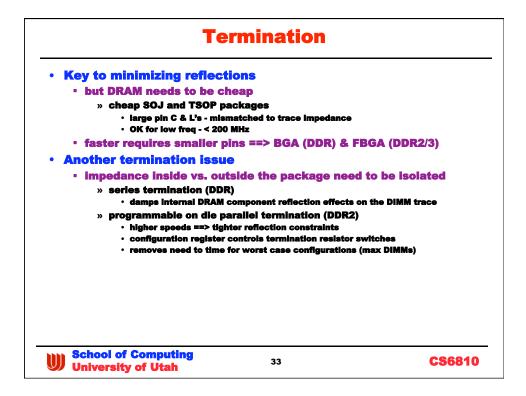

| Sigr                                                                                                                                                                      | nal Integrity        |                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|

| • Increasingly limiting in s                                                                                                                                              | hrinking processes   | •                |

| <ul> <li>gets even worse</li> </ul>                                                                                                                                       |                      |                  |

| » as speeds increase                                                                                                                                                      |                      |                  |

| » as trace length increas                                                                                                                                                 |                      |                  |

| <ul> <li>Multi-drop wires are a pr</li> </ul>                                                                                                                             |                      |                  |

| <ul> <li>very difficult to achieve<br/>practice</li> </ul>                                                                                                                | perfect transmission | line behavior in |

| <ul> <li>&gt; Impedance changes wi</li> <li>• temperature</li> <li>• manufacturing variabi</li> <li>• L &amp; C effects of the n</li> <li>• signal reflections</li> </ul> | llity                |                  |

| <ul> <li>signal reflections</li> <li>result is signal distortio</li> </ul>                                                                                                | n                    |                  |

| <ul> <li>made worse by noise</li> <li>also a neighborhood p</li> </ul>                                                                                                    |                      |                  |

| <ul> <li>DRAM systems</li> </ul>                                                                                                                                          |                      |                  |

| <ul> <li>traces are long, and bro</li> <li>intra- and inter-device</li> </ul>                                                                                             | adcast is the norm   |                  |

|                                                                                                                                                                           |                      |                  |

| School of Computing<br>University of Utah                                                                                                                                 | 30                   | CS6810           |

|        | endor c<br>» keep | ng up<br>es availa<br>choice<br>inside th<br>ven though | e 64 ms i | refresh p      | eriod    | m mem   | огу                |                     |

|--------|-------------------|---------------------------------------------------------|-----------|----------------|----------|---------|--------------------|---------------------|

|        |                   | Device<br>Capacity                                      |           |                | Row Size | Refresh |                    |                     |

| Family | Vdd               | Mb                                                      | # Banks   | # Rows         | kB       | Count   | t <sub>ec</sub> ns | t <sub>eec</sub> ns |

| DDR    | 2.5V              | 256                                                     | 4         | 8192           | 1        | 8192    | 60                 | 67                  |

|        |                   | 512                                                     | 4         | 8192           | 2        | 8192    | 55                 | 70                  |

|        | 1.8V              | 256                                                     | 4         | 8192           | 1        | 8192    | 55                 | 75                  |

| DDR2   |                   | 512                                                     | 4         | 16384          | 1        | 8192    | 55                 | 105                 |

| DDR2   |                   |                                                         |           | 46004          | 1        | 8192    | 54                 | 127.5               |

| DDR2   |                   | 1024                                                    | 8         | 16384          | _        |         |                    |                     |

| DDR2   |                   |                                                         | 8<br>8    | 16384<br>32768 | 1        | 8192    | ~                  | 197.5               |

| DRAM chip<br>type      | DIMM Stick<br>Type     | Bus Clock<br>Rate<br>(MHz) | Memory<br>Clock<br>Rate<br>(MHz) | Channel<br>Bandwidth<br>(GB/s) | non-ECC<br>Channel<br>Width | ECC<br>Channel<br>Width | Prefetch<br>Buffer<br>Width | Vdd        | Read<br>Latency<br>Typical<br>(bus<br>cycles) | DIMM<br>pins |

|------------------------|------------------------|----------------------------|----------------------------------|--------------------------------|-----------------------------|-------------------------|-----------------------------|------------|-----------------------------------------------|--------------|

| DDR-200                | PC-1600                | 100                        | 100                              | 1.6                            | 64                          | 72                      | 2                           | 2.5        | 2-3                                           | 184          |

| DDR-266                | PC-2100                | 133                        | 133                              | 2.133                          | 64                          | 72                      | 2                           | 2.5        | 2-3                                           | 184          |

| DDR-333<br>DDR-400     | PC-2700<br>PC3200      | 167<br>200                 | 167<br>200                       | 2.667<br>3.2                   | 64<br>64                    | 72<br>72                | 2<br>2                      | 2.5<br>2.5 | 2-3<br>2-3                                    | 184<br>184   |

| DDR2-400               | PC2-3200               | 100                        | 200                              | 3.2                            | 64                          | 72                      | 4                           | 1.8        | 3-9                                           | 240          |

| DDR2-533               | PC2-4200               | 133                        | 266                              | 4.267                          | 64                          | 72                      | 4                           | 1.8        | 3-9                                           | 240          |

| DDR2-667<br>DDR2-800   | PC2-5300<br>PC2-6400   | 167<br>200                 | 333<br>400                       | 5.333<br>6.4                   | 64<br>64                    | 72<br>72                | 4<br>4                      | 1.8<br>1.8 | 3-9<br>3-9                                    | 240<br>240   |

| DDR2-800               | PC2-6400               | 200                        | 400                              |                                | 64                          |                         | 4                           | 1.8        | 3-9                                           | 240          |

| DDR3-800               | PC3-6400               | 100                        | 400                              | 6.4                            | 64                          | 72                      | 8                           | 1.5        | ?                                             | 240          |

| DDR3-1066              | PC3-8500               | 133                        | 533                              | 8.53                           | 64                          | 72                      | 8                           | 1.5        | ?                                             | 240          |

| DDR3-1333<br>DDR3-1600 | PC3-10600<br>PC3-17000 | 167<br>200                 | 667<br>1066                      | 10.67<br>18.06                 | 64<br>64                    | 72<br>72                | 8<br>8                      | 1.5<br>1.5 | ?                                             | 240<br>240   |

|                        |                        |                            |                                  |                                |                             |                         | -                           |            | ·                                             |              |

| Conclu                                                                | iding Remarl         | ks                |

|-----------------------------------------------------------------------|----------------------|-------------------|

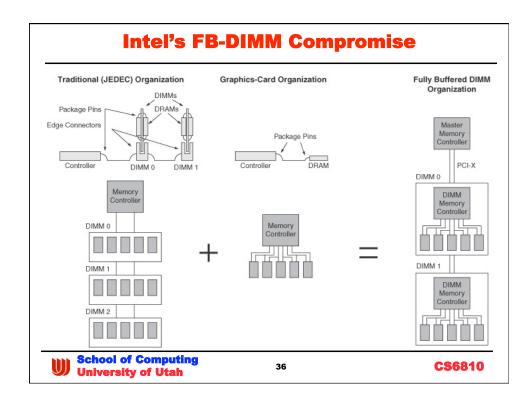

| • Whirlwind tour – phew                                               | 1                    |                   |

| • Take homes                                                          |                      |                   |

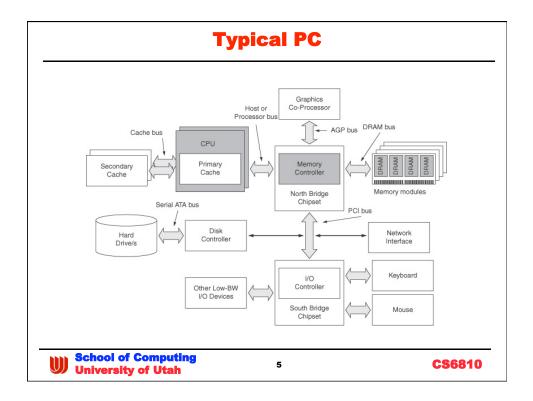

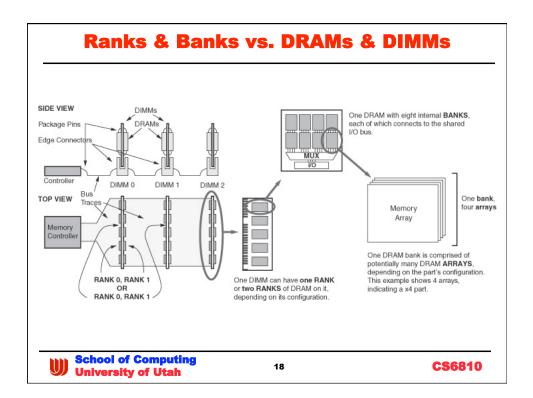

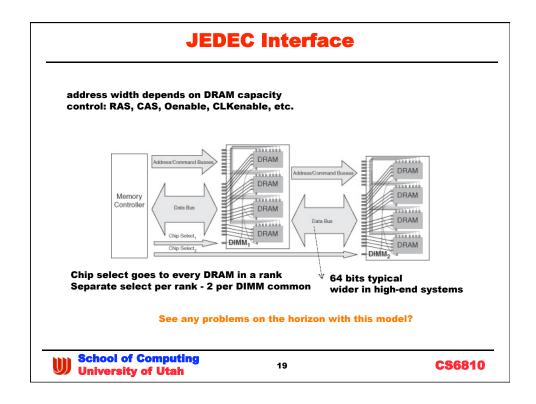

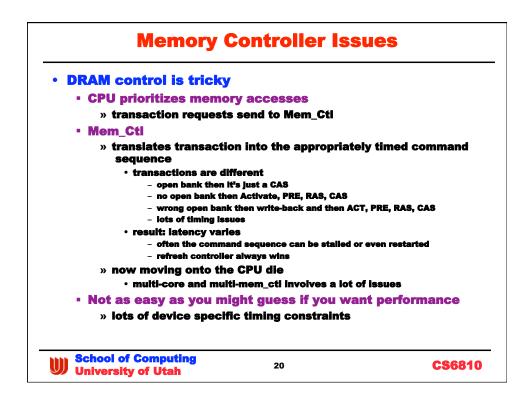

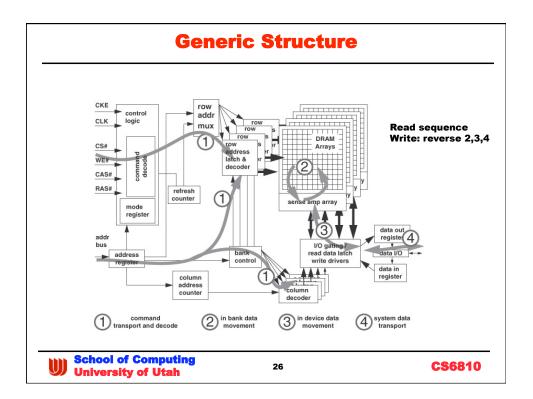

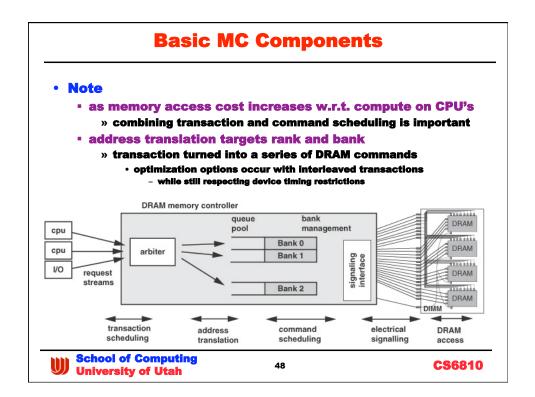

| <ul> <li>understand role of MC</li> </ul>                             | C, channel, rank, ba | nk, row & column  |

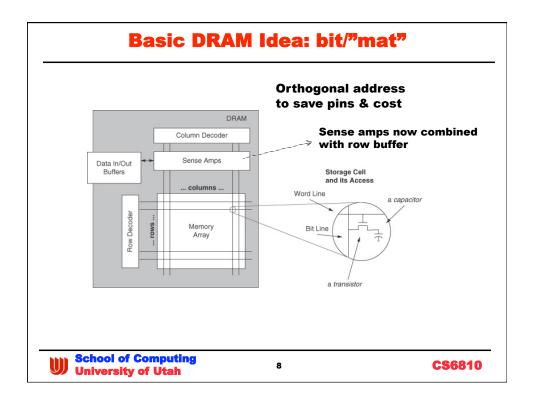

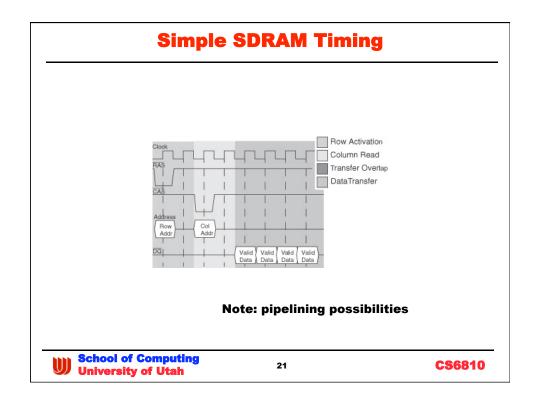

| <ul> <li>large mat delay &amp; bro</li> </ul>                         | adcast commands      |                   |

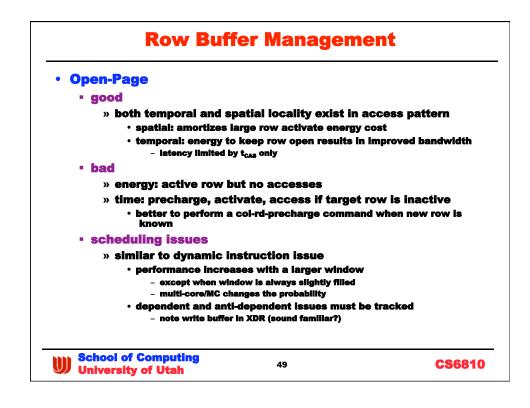

| » MC role is to overla                                                | p commands optimally | /                 |

| » best bandwidth → k                                                  | •                    |                   |

| » open and closed rov                                                 | •••••                | ea                |

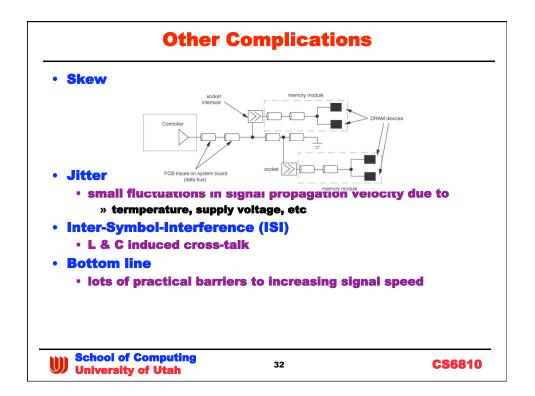

| challenges for the fut                                                |                      |                   |

| » signal integrity limit » cpu pin count limits                       | -                    |                   |

| Multi-core and improve                                                |                      | ology             |

| <ul> <li>only makes things water</li> </ul>                           | orse                 |                   |

| <ul> <li>more compute power</li> <li>» caches help and are</li> </ul> | e critical           | pressure          |

| » but they can't catch                                                |                      |                   |

| • power is and will con                                               | tinue to de a tundai | mental constraint |

| School of Computing<br>University of Utah                             | 50                   | <b>CS6810</b>     |