**Segments (cont'd)**

» more diversity in performance and energy efficiency than netbook

market rapidly slowing due to netbook, laptop, and server

» with a network the screen, keyboard, and compute gizmo's need not be co-located

» diverse motherboard capability (performance, memory, etc.)

11

nance compromised for energy efficiency

• cheap, light, and a bigger screen than a cell phone

» battery life is a key issue

ssor perfe

• a bit heavier and more expensive

» processor and system cost: 2-5x netbook

» \$50 - \$1000 processor, 5-10x more for system

• pr

expansion

School of Computing University of Utah

Netbook

• Laptop

• Desktop

10

CS6810

CS6810

| Intent of the Course                                                                                                                          |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---|

| Provide a foundation for future professional activity                                                                                         | • |

| <ul> <li>at least 3 possible goals</li> </ul>                                                                                                 |   |

| » understanding the compute platform that you use <ul> <li>key to achieving highly efficient code for SW types</li> </ul>                     |   |

| ISA and organization are what you care about                                                                                                  |   |

| » research into new architectural options                                                                                                     |   |

| <ul> <li>key academic role &amp; possible thesis area preparation</li> </ul>                                                                  |   |

| <ul> <li>ISA, organization, and high level understanding of hardware<br/>constraints will be needed</li> </ul>                                |   |

| » design of new systems                                                                                                                       |   |

| <ul> <li>perhaps the ultimate relevance</li> </ul>                                                                                            |   |

| <ul> <li>further courses will be needed to finish this process</li> <li>VL8) &amp; embedded systems courses will be your next step</li> </ul> |   |

| all 3 will are important     _ In much greater depth                                                                                          | • |

| OK that's the sales pitch                                                                                                                     |   |

| <ul> <li>for why you should care</li> </ul>                                                                                                   |   |

|                                                                                                                                               |   |

| NN School of Computing                                                                                                                        | - |

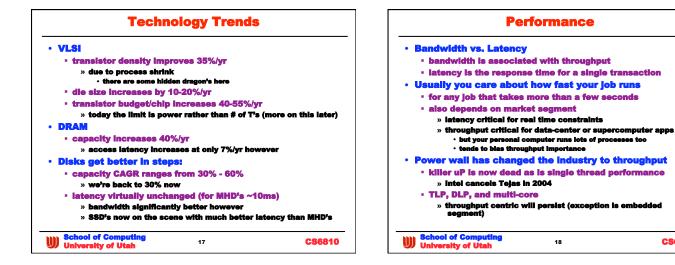

**Bandwidth Optimization Results**

Micropr

10

Relative latency improvement

19

Latency improvement = andwidth improvement

100

CS6810

10.000

1000

100

elative

School of Computing University of Utah

Performance

18

**CS6810**

| Power Fund                                                                       | lamentals                    |    |

|----------------------------------------------------------------------------------|------------------------------|----|

| • 2 components:                                                                  |                              |    |

| <ul> <li>active – power consumed wh</li> </ul>                                   | en something is happening    |    |

| <ul> <li>leakage – power consumed li</li> </ul>                                  | ndependent of activity       |    |

| <ul> <li>P<sub>total</sub> = P<sub>active</sub> + P<sub>leakage</sub></li> </ul> |                              |    |

| • Pactive = $\alpha CV^2 f$                                                      |                              |    |

| <ul> <li>hence linear with frequency</li> </ul>                                  |                              |    |

| Pleakage goes up 10x with e                                                      | verv process step            |    |

| • process & circuit tricks have                                                  | mitigated this significantly |    |

| » how many one-trick ponies a                                                    | are in the stable            |    |

| <ul> <li>additional ~2x w/ every 10 C</li> </ul>                                 | temperature dependence       |    |

| » also dependent on Vdd-Vth                                                      |                              |    |

| » actual equation is quite hair,                                                 | У                            |    |

| <ul> <li>Voltage scaling</li> </ul>                                              |                              |    |

| <ul> <li>quadratic benefit for P<sub>active</sub></li> </ul>                     |                              |    |

| <ul> <li>problem for P<sub>leakage</sub></li> </ul>                              |                              |    |

| <ul> <li>today there is little room for</li> </ul>                               | Vdd scaling                  |    |

| School of Computing<br>University of Utah                                        | 23 <b>CS68</b>               | 10 |

| <b>Concluding Re</b> | emarks |

|----------------------|--------|

|----------------------|--------|

• It's important to keep several things in mind when a design decision is made · cost and area issues • totally new means new verification tactics » an increasing component of design cost • power and performance trade-off • What's the right metric - depends on what you care about · Ideally you want more performance & less power for the work that you care about • Note • power is an instantaneous, work independent metric · consider » Q = energy x delay" (more realistic measure of design quality) » adjust n for your blas

• embedded n=1 typical, n=2 often used for performance oriented systems School of Computing University of Utah **CS6810** 29