6

**CS6810**

## Latency ala SGI Origin O3K

#### • 500 MHz CPU

• model lacks contention and occupancy effects

» e.g. measured unloaded – hence best case

» DSM has striking impact on communication load

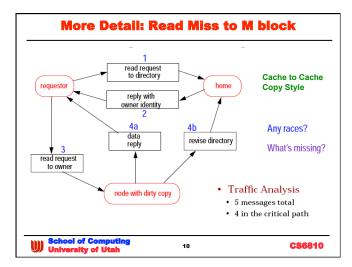

| Characteristic                                             | CPU clocks <=<br>16 PE's | CPU clocks 17-64<br>PE's |

|------------------------------------------------------------|--------------------------|--------------------------|

| Cache Hit                                                  | 1                        | 1                        |

| Miss to Local Memory                                       | 85                       | 85                       |

| Remote Miss served by Home                                 | 125                      | 150                      |

| Remote Miss served by Remote \$<br>(known as a 3-hop miss) | 140                      | 170                      |

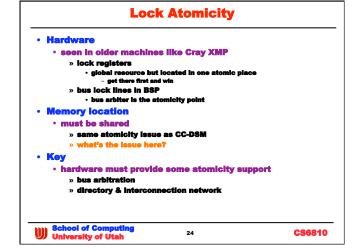

more of an interconnect property than an instruction set issue » bus hold bus after read, modify if unlocked, release bus problems

– holding bus increases bus bottleneck likelihood » distributed interconnect Test & Set instruction • read value but set location to 1 (  $1 \rightarrow$  locked) » less occupancy than RMW » if return value is 1 then previous lock exists so try again other variants » swap: exchange register value with a memory location School of Computing University of Utah

25

**Lock Algorithm Goals**  Low latency quick when not contention - slower if there's competition - fact of life Low occupancy minimize amount of interconnect traffic • Scalability • no worse than linear traffic and latency increase Low storage overhead • minimize meta-data • Fairness · hard to be truly fair • redefine as starvation free » e.g. guarantee that requester will never wait forever School of Computing University of Utah 26 **CS6810**

**CS6810**

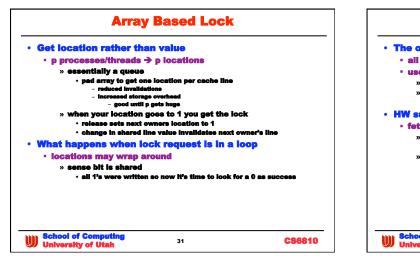

# **More Advanced Goals**

- Reduced contention?

- need some back-off model to desynchronize

- » e.g. ethernet exponentional back-off idea

- On lock release

- #1 have only one waiting process try for the lock

- » also reduces contention

- #2 have only one waiting process incur a read miss

- Enter more advanced protocols

- ticket lock does #1

- array based lock does both

- both are fair in that they effectively create a FIFO grant order

29

School of Computing University of Utah

**CS6810**

### **Ticket Lock** • Take a number each process reads lock and gets next number » from a number serving variable » next requester invalidates you but you have your number read the "now serving" variable » normal reads so no invalidation until the number changes » read your number then go • release » update the now-serving number » "fetch & increment" • one instance of fetch & op hardware support optimization » delay next read based on difference between • your number and "now serving" variable School of Computing University of Utah 30 CS6810

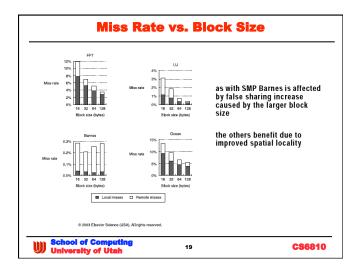

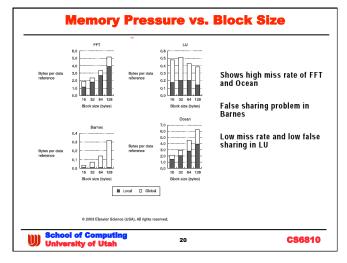

| Implications for Software                                                                                                                                                                                                                                                  | Concluding Rema                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Computation phases         <ul> <li>maximize locality and minimize interconnect traffic</li> </ul> </li> <li>Data allocation         <ul> <li>pad to</li> <li>minimize faise sharing &amp; align on cache line boundary             <ul></ul></li></ul></li></ul> | <ul> <li>For large parallel machines         <ul> <li>DSM may have become extinct</li> <li>SUN was the last to go</li> <li>SUN was the last to go</li> <li>IBM, Cray, HP, Dell, move to message                 <ul></ul></li></ul></li></ul> |

| School of Computing<br>University of Utab 33 CS6810                                                                                                                                                                                                                        | University of Utab 34                                                                                                                                                                                                                         |

# nct to message passing power is saved

**Remarks**

**CS6810**