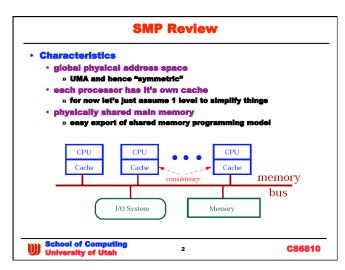

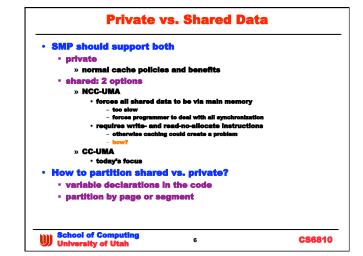

## Private vs. Shared Data • SMP should support both • private » normal cache policies and benefits • shared: 2 options » NCC-UMA • forces all shared data to be via main memory • too slow • forces programmer to deal with all synchronization • requires write- and read-no-allocate instructions • othervies eaching could create a problem • how? » CC-UMA • today's focus • How to partition shared vs. private?

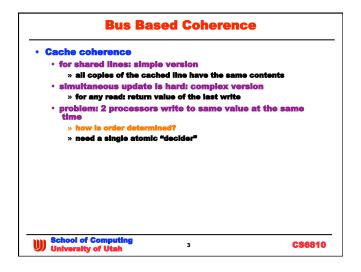

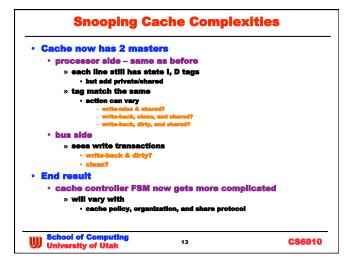

## **Coherence Implications**

- Additional cost

- caches now need to snoop the bus

- » watch for writes, tag compare and "update" if they have a copy

- Ordering constraints

- · reordering reads is OK

- » but not involving writes

- · writes must finish in program order

- » EVEN if they are independent

- ncy in the othe · since there may be a hidden dep

- · also because cache management is by line not variable

- » this can be relaxed

- · more on this later

CS6810

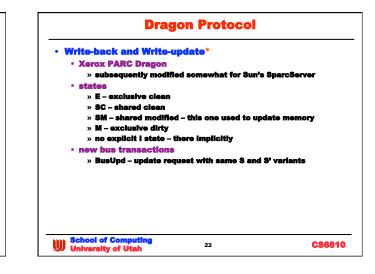

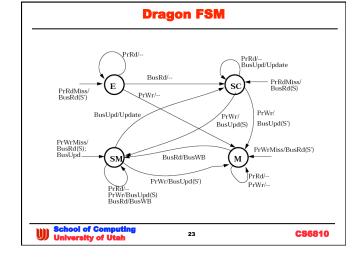

### **2 SMP Protocol Options**

- Write-invalidate

- writer needs exclusive copy

- » write forces other copies to be invalidated

- » next read by others is a miss and they get new fresh line

- - » one win's bus arbitration and the "decider" has spoken

- bus broadcast

- » doesn't need to broadcast write value only address

- Write-update

- · broadcast write value & address

- If other copies exist

- » then appropriate line is updated

- · What haven't we considered so far?

- · hint: LOTS

CS6810

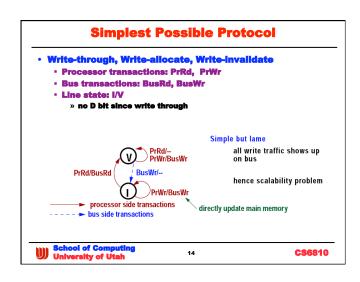

### **Consider All Cases**

- X product

- · (read, write) (miss, hit) (valid copy in cache, memory)

- · (write invalidate, write update)

- Simple with write-through caches

- · memory always has an updated copy

- new writer gets valid copy

- » either by cache to cache transfer or from memory

- · Harder with write-back caches

- good idea if cache is mostly holding private data

- » but memory may not be up to date

- · force invalidate of write back to memory

- rores invaluate or write back to memory

anop grabs latest copy

cache-to-cache copy and no-update of memory

if write update and previous owner keeps copy then must clear D bit

keys only 1 D-bit can exist max > single "exclusive" owner

- What happens?

- write miss, read miss

11

CS6810

### **Performance Issues**

- Too many to exhaustively list

- Key protocol choice issues

- · multiple writes to the same line write invalidate

- » less bus traffic

- · 1st write → bus invalidate

- subsequent writes are kept local

as long as there is a write hit

- » typically Wr-inv is best choice · when line is hamm ored by one processor at a time

- write-update

- » every write generates bus traffic

- us scalability is an issue so it easily saturates

- » still it wins when

- a certain line is being hammered by multiple proce

and when there is 1 writer and the rest are consumers

- **Programs share variables not cache lines**

- · Issues?

School of Computing University of Utah

12

CS6810

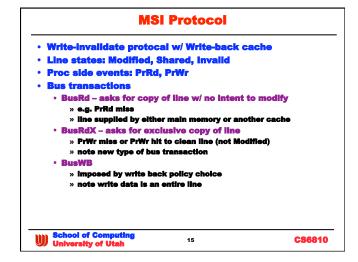

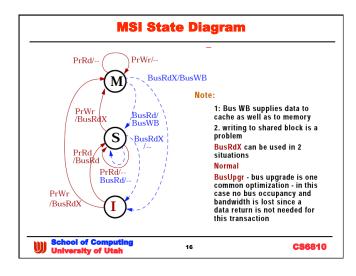

## **MSI Analysis**

- write completion » BusRdX & data return complete

- bus atomicity "decider point" makes this easy

- » other cache snoopers can see when their pending write is issued when the controller wins arbitration

- Other options

• Seq. Consistency

- BusRd in M: go to I rather than S

- » migratory protocol line always just migrates to writer

- » tradeoff

- · another owner likely to write soon then I is better

- · old owner likely to read soon then S is better

- » hybrid is possible with extra protocol bit

- choice of Sequent Symmetry and MIT Alewife machine

flexibility potential for increased cost & performance

question is how much of each?

School of Computing University of Utah

CS6810

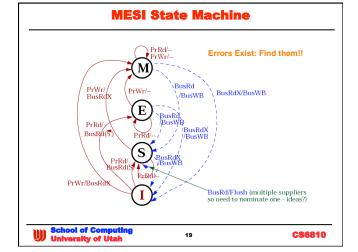

### **MESI Protocol**

- Add Exclusive state

- deals w/ PrRd followed by PrWr problem

- · meanings change a bit

- » E = exclusive clean memory is consistent

- » M = exclusive dirty memory is inconsistent

- » S = 2 or more sharers, no writers, memory consistent

- » I = same as always

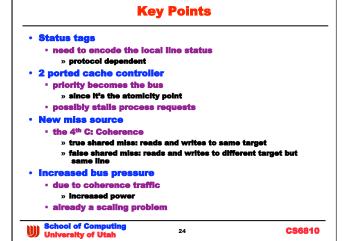

- New S semantics adds an additional problem

- a shared signal must be added to the bus

- » single wired-OR wire is sufficient

- note scaling problem doesn't work well at today's frequencies

- » BusRd(S) shared signal asserted

- » BusRd(S') shared signal not asserted

- » BusRd means don't care about shared signal

- » FLUSH optional for cache to cache copy?

CS6810

CS6810

## Flush Issues · don't want redundant suppliers when a new sharer comes on line » last exclusive owner knows who they are » so that one does the flush » If no sharing then supplied from memory · complicates bus Stanford Dash & SGI Origin series choice What haven't we worrled about yet? School of Computing University of Utah

20

**MESI Analysis**

# • Flush Issues • don't want redundant suppliers when a new sharer comes on line » last exclusive owner knows who they are » so that one does the flush » if no sharing then supplied from memory • complicates bus • Stanford Dash & SGI Origin series choice • What haven't we worried about yet? • what happens when a line gets victimized? » exercise to figure out the new state machine

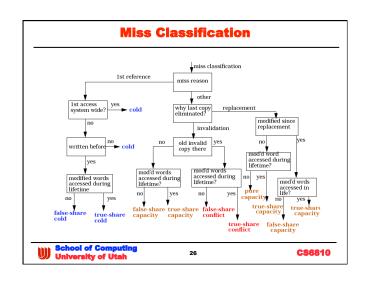

# Classifying Misses • For a particular reference stream • define the lifetime for a block in the cache • do per word accounting » e.g. remote reference from processor x causes eviction • Ideas for how to do this?

### **Getting More Real** • 2 level cache hierarchy is likely Harvard L1\$ · Unified L2 · L2 is the one that sits on the bus now · L2 is coherent but what about L1's » L1 write and read misses don't cause much problem • percolate through to L2 and then the rest is similar » L1 read hit - no problem » L1 write hit · write has to percolate all the way to the bus L2 line eviction » due to invalidate $\,$ » L2 needs to pass eviction up and evict L1's entry More synchronization through the cache hierarchy will slow things down » question is how much School of Computing University of Utah CS6810 27