| Reduce Hit Time                                                    |                                     |                |  |  |

|--------------------------------------------------------------------|-------------------------------------|----------------|--|--|

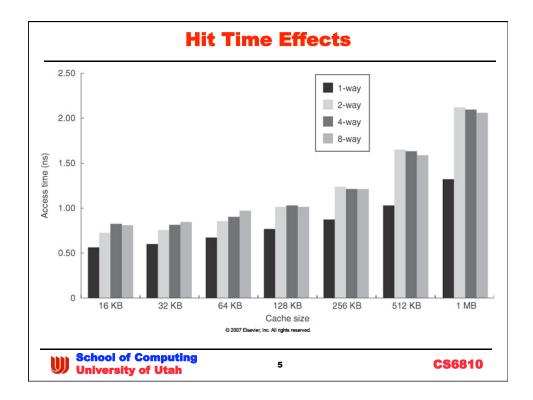

| • Small and simple cach                                            | les                                 |                |  |  |

| keep cache hierarchy                                               | on chip                             |                |  |  |

| » off chip access is 10                                            | <b>)-100x penalty</b>               |                |  |  |

| <ul> <li>small, direct-mapped</li> </ul>                           |                                     |                |  |  |

| » note L1\$ size doesn                                             | 't change much w/ tec               | hnology        |  |  |

| » L2 is where the bigg                                             | jest change occurs                  |                |  |  |

| <ul> <li>associativity is a double</li> </ul>                      | ble edged sword                     |                |  |  |

| • Next slide                                                       |                                     |                |  |  |

| • models based on CAC                                              | TI                                  |                |  |  |

| » common research to                                               | ool                                 |                |  |  |

| » book model is CACT                                               | 1-IV                                |                |  |  |

|                                                                    | ccurately deal w/ wire de           | lay            |  |  |

| <ul> <li>current version is 6</li> <li>much better wird</li> </ul> | 9.5<br>e models – SPICE back annota | ted validation |  |  |

| » undecided                                                        |                                     |                |  |  |

| <ul> <li>might be used in H</li> </ul>                             | W4                                  |                |  |  |

|                                                                    |                                     |                |  |  |

| School of Computing<br>University of Utah                          | 4                                   | <b>CS6810</b>  |  |  |

| <b>Reduce Miss Penalty</b>                                |                     |         |  |  |

|-----------------------------------------------------------|---------------------|---------|--|--|

| Critical word first                                       |                     |         |  |  |

| <ul> <li>overlap transfer with a</li> </ul>               | ability to use data |         |  |  |

| <ul> <li>complicates next leve</li> </ul>                 | access              |         |  |  |

| » not all that bad                                        |                     |         |  |  |

| » at DRAM level                                           |                     |         |  |  |

| • MEM_CTL in the wa                                       |                     |         |  |  |

| overhead to suppor                                        |                     |         |  |  |

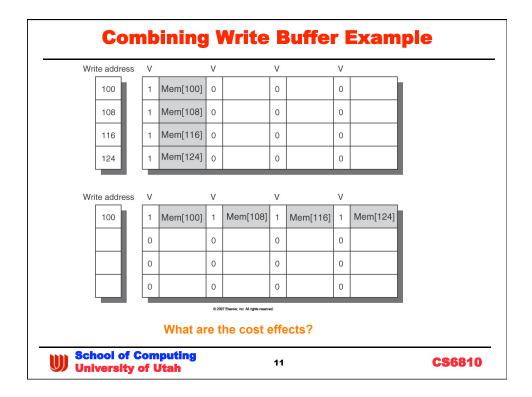

| Coalesce/Combining/M                                      |                     |         |  |  |

| <ul> <li>writes happen from a</li> </ul>                  | register value      |         |  |  |

| <ul> <li>cache lines bigger</li> </ul>                    |                     |         |  |  |

| » so buffer writes by c                                   |                     |         |  |  |

| » same unit of transfer<br>• cache to cache               | r                   |         |  |  |

| <ul> <li>cache to Cache</li> <li>cache to DRAM</li> </ul> |                     |         |  |  |

|                                                           |                     |         |  |  |

|                                                           |                     |         |  |  |

|                                                           |                     |         |  |  |

| School of Computing<br>University of Utah                 | 10                  | C\$6810 |  |  |

| Ancillary Caches                                                               |                                       |         |  |  |

|--------------------------------------------------------------------------------|---------------------------------------|---------|--|--|

| • Victim cache (Jouppi)                                                        |                                       |         |  |  |

| <ul> <li>small cache to hold v</li> </ul>                                      | victimized lines                      |         |  |  |

| <ul> <li>idea allows arbitrary</li> <li>» total extra associat</li> </ul>      | · · · · · · · · · · · · · · · · · · · |         |  |  |

| <ul> <li>downside</li> </ul>                                                   |                                       |         |  |  |

| » parallel check of reg<br>» fully associative                                 | gular and victim                      |         |  |  |

| • Trace cache (Weiser,                                                         | Peleg)                                |         |  |  |

| • Intel P4                                                                     |                                       |         |  |  |

| » expensive – many in                                                          | struction copies                      |         |  |  |

| • Assist cache (HP and                                                         | somebody you kn                       | iow)    |  |  |

| <ul> <li>1<sup>st</sup> touch goes to assi</li> </ul>                          | ist                                   |         |  |  |

| <ul> <li>2<sup>nd</sup> touch goes to reg<br/>» makes prefetch less</li> </ul> |                                       | e cache |  |  |

| • downside                                                                     |                                       |         |  |  |

| » similar to victim ca                                                         | che                                   |         |  |  |

| School of Computing<br>University of Utah                                      | 20                                    | CS6810  |  |  |

| Technique                                | Miss<br>Rate | Miss<br>Penalty | Hit<br>Time | HW<br>Complex<br>ity | Comments                                                                |

|------------------------------------------|--------------|-----------------|-------------|----------------------|-------------------------------------------------------------------------|

| Larger Cache                             | win          |                 | lose        | easy                 | cost is approx. linear                                                  |

| Larger Block Size                        | win          | lose            |             | easy                 | trivial engineering effort                                              |

| Higher Associativity                     | win          |                 | lose        | 1                    | associative match isn't free                                            |

| Victim Caches                            | win          |                 |             | 2                    | e.g. HP 7200                                                            |

| Pseudo-Associative                       | win          |                 |             | 2                    | Used in L2 of MIPS R10000                                               |

| HW Prefetch of I and D                   | win          |                 |             | 2                    | D fetch hard to do correctly                                            |

| Compiler controlled prefetch             | win          |                 |             | 3                    | Needs non-blocking cache                                                |

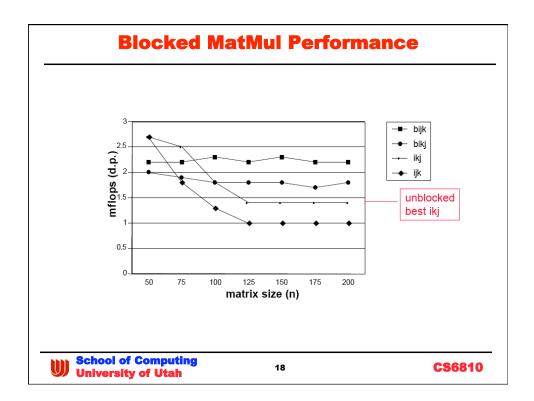

| Compiler cache scheduling<br>(blocking,) | win          |                 |             | 0                    | Too bad it's hard to do for<br>all applications - loop focus<br>for now |

| Technique                              | Miss<br>Rate | Miss<br>Penalty | Hit<br>Time | HW<br>Complex<br>ity | Comments                              |

|----------------------------------------|--------------|-----------------|-------------|----------------------|---------------------------------------|

| Prioritizing Read Misses               |              | win             |             | 1                    | write buffer - simple                 |

| Subblock placement                     |              | win             |             | 1                    | good at reducing tag<br>overhead      |

| Early restart + critical word<br>first |              | win             |             | 2                    | MIPS R10K, IBM 620                    |

| Nonblocking Caches                     |              | win             |             | 3                    | MIPS R10K, AXP 21064                  |

| Second Level Caches                    |              | big win         |             | 2                    | big additional cost for all that SRAM |

| Small Simple Caches                    | lose         |                 | win         | 0                    | trivial so it's widely used           |

| Avoid translation effects              |              |                 | win         | 2                    | AXP 21064<br>several PA-whatevers     |

| Pipelining Writes                      |              |                 | win         | 1                    | AXP 21064, PA-8000,<br>UltraSPARC     |