## Locality

- 2 basic types

- temporal

- » If you used this block then you will use it again soon

- spatial

- » If you used this block you will use a nearby one soon

- Exploiting locality

- match of application memory usage and cache design

- some codes are touch once

- » encrypt/decrypt, encode/decode, ...

- » here caches are a liability

School of Computing University of Utah

CS6810

### Locality

- 2 basic types

- temporal

- » If you used this block then you will use it again soon

- spatial

- » If you used this block you will use a nearby one soon

- Exploiting locality

- match of application memory usage and cache design

- » If you match you win simple as that

- some codes are touch once → fall through misses

- » e.g. encrypt/decrypt, encode/decode, ... (media influence)

- » here caches are a liability

- you have to swing to miss

try L1 miss? try L2 miss? ...

- a lot of extra time if you end up going to DRAM anyway

- historical tidbit

- » Seymour Cray didn't believe in caches or DRAM

- · or even 2's complement initially

School of Computing University of Utah

CS6810

#### **Performance Issues**

- Basics

- $CPUtime = IC * CPI * cycle_time$

$$CPI = \frac{1}{frequency}$$

$$IPC = \frac{1}{CPI}$$

$CPUtime = \frac{1}{IPC * frequency}$ IC

- Enter stalls

- IPC gets degraded by stalls

- » we've seen stalls due to hazards and pipeline issues

- » now the focus is on memory stalls

- · influence is based on load & store %

- with good branch prediction most stalls are men

7

School of Computing University of Utah

CS6810

# **Computing Memory Effect**

- Misses induce stalls

- ILP & TLP can overlap some of the penalty

- » but a miss is a surprise so some of the penalty won't be hidden

XEQtime = (CPUcycles + MEMstallcycles) \* cycle\_time

MEMstallcycles = num\_misses \* miss\_penalty

$MEM stall cycles = IC * \frac{misses}{instruction} * miss\_penalty$

$MEMstallcycles = IC * \frac{memory\_accesses}{\vdots \vdots \vdots \vdots \vdots \vdots} * miss\_rate * miss\_penalty$ instruction

Separate

$MEM stall cycles = \sum READ stalls, Write stalls$

$READ stalls = IC * \frac{reads}{instruction} * read\_miss\_rate * read\_miss\_penalty$

$WRITE stalls = IC * \frac{writes}{instruction} * write\_miss\_rate * write\_miss\_penalty$

School of Computing University of Utah

8

CS6810

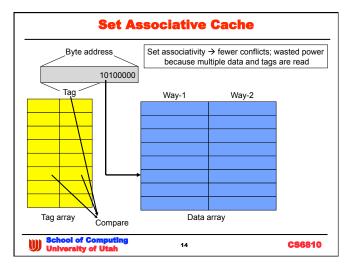

## **Increasing Associativity** Data and Tag RAM" #\_entries the same will depend on capacity Logic involved in compares • for n ways → n parallel compares » If one of the succeeds then hit in the associated way » If none succeed then miss » If >1 succeeds somebody made a big mistake » If n is large then problems $\rightarrow$ way prediction fully associative » huge number of parallel compares (m line capacity $\rightarrow$ m compares power hungry - limits use to smallish caches ike a TLB » or save power but increase hit-time · n compares where n << m N compares where it is a like it is a like it is very long stop when you find a hit but miss time is VERY long variable miss time but in essence this is always true anyone. CS6810

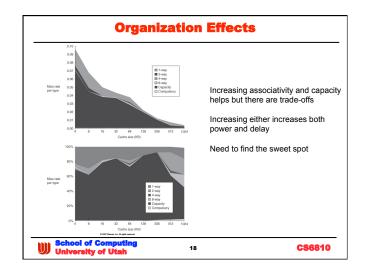

#### **Optimizations to Reduce Miss Rate**

- Increase block size

- +: reduces tag size, compulsory misses, and miss rate if there is spatial locality

- -: miss must fetch larger block, no spatial locality → waste, increases conflict misses since for same capacity there will be less blocks in the cache

- Increase cache size

- +: reduces conflict and capacity misses

- -: larger caches are slower increased hit time

- Increased associativity

- · Issues already discussed

- rule of thumb 2-way associativity w/ capacity N/2 has the same miss rate as 1-way size N cache

- Way prediction

- · can use methods similar to branch prediction

- » get it right and reduce power consumption since

- 1 way SA = direct mapped

19

CS6810

# **Hiding/Tolerating Miss Penalty**

- 000 execution

- combo of ILP and TLP techniques

- · do as much as you can in between a load and consumer

- Non-blocking caches

- first miss doesn't block subsequent actions

- cache controller keeps track of multiple outstanding misses

- » MSHR's miss status handling registers & dynamic issue req'd

- Write buffers

- prioritize reads handle writes when memory is otherwise idle

20

- » opposite of itanium ALAT concept

- » reads must check write buffer to get latest result

- Prefetching (even if you get it right)

- too aggressive → increased cache pressure

- possible to increase conflict/capacity misses

School of Computing University of Utah

CS6810

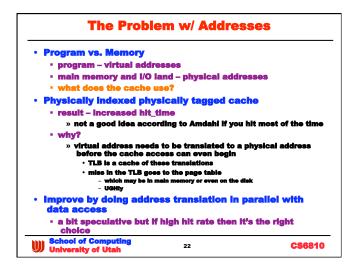

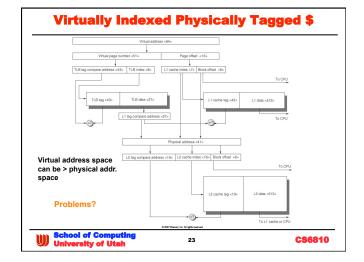

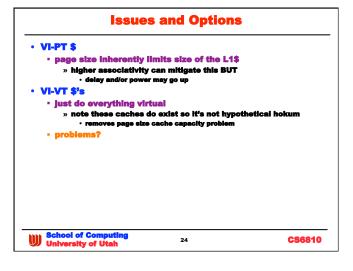

# **Issues and Options**

- VI-PT \$

- page size inherently limits size of the L1\$

- » higher associativity can mitigate this BUT

- · delay and/or power may go up

- VI-VT \$'s

- Just do everything virtual

» note these caches do exist so it's not hypothetical hokum · removes page size cache capacity proble

- - » multiple processes concurrently running

08 guarantees address space privacy

- - » assign process to an address space ID

- » address space part of tag RAM space ID provided w. virtual address

- processes are not interleaved like threads so process ID is known

on context switch OS must flush cache if AS-ID isn't active

School of Computing University of Utah

CS6810

# **Concluding Remarks**

- This lecture somewhat remedial

- but essential to understand what follows

- » If you don't

- read the book more thoroughly or go back to the ca3810 text

ask questions, confer w/ Dogan, ....

- » mid-term questions will be conceptual

- » subsequent homework will be more substantive Applies to reality as well

- lots of cores complicate cache design

- » foundation however is the same

School of Computing University of Utah

CS6810

Page 7