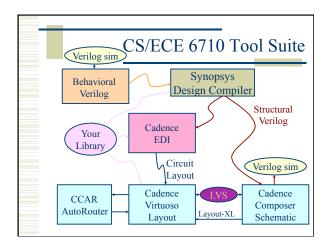

### Synthesis and Place & Route Synopsys design compiler Cadence Encounter Digital Implementation System (EDI)

### **Design Compiler**

- Synthesis of behavioral to structural

- Three ways to go:

- 1. Type commands to the design compiler shell

- Start with syn-dc and start typing

- Write a script

- Use syn-script.tcl as a starting point

- 3. Use the Design Vision GUI

- · Friendly menus and graphics...

### Design Compiler – Basic Flow

- 1. Define environment

- target libraries your cell library

- synthetic libraries DesignWare libraries

- link-libraries libraries to link against

- 2. Read in your structural Verilog

- Usually split into analyze and elaborate

- 3. Set constraints

- timing define clock, loads, etc.

### Design Compiler - Basic Flow

- 4. Compile the design

- · compile or compile\_ultra

- · Does the actual synthesis

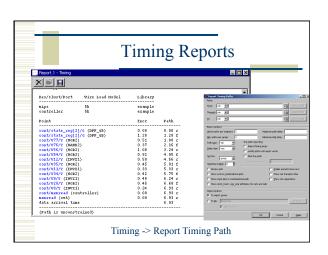

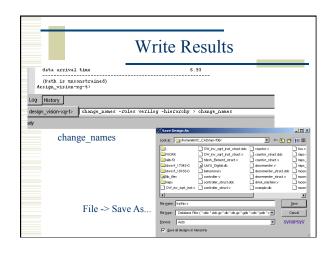

- 5. Write out the results

- · Make sure to change names

- Write out structural verilog, report, ddc, sdc files

### beh2str – the simplest script!

# beh2str script

set target\_library [list [getenv "LIBFILE"]]

set link\_library [concat [concat "\*" \$target\_library] \$synthetic\_library]

read\_file -f verilog [getenv "INFILE"]

#/\* This command will fix the problem of having \*/

#/\* assign statements left in your structural file. \*/

set\_fix\_multiple\_port\_nets -all -buffer\_constants

compile -ungroup\_all

check\_design

#/\* always do change\_names before write... \*/

redirect change\_names { change\_names -rules verilog -hierarchy verbose }

write -f verilog -output [getenv "OUTFILE"]

# .synopsys\_dc.setup set SynopsysInstall [getenv "SYNOPSYS"] set search\_path [list .\ [format "%s%s" \$SynopsysInstall /libraries/syn] \ [format "%s%s" \$SynopsysInstall /dw/sim\_ver] \ ] define\_design\_lib WORK -path ./WORK set synthetic\_library [list dw\_foundation.sldb] set synlib\_wait\_for\_design\_license [list "DesignWare-Foundation"] set link\_library [concat [concat "\*" \$target\_library] \$synthetic\_library] set symbol\_library [list generic.sdb]

### What beh2str leaves out...

- Timing!

- No clock defined so no target speed

- No input drive defined so assume infinite drive

- No output load define so assume something

### \* /uusoc/facility/cad\_common/local/class/6710/F11/synopsys #/\* search path should include directories with memory .db files \*/ #/\* as well as the standard cells \*/ set search\_path [list .\ [format "%s%s" SynopsysInstall /libraries/syn] \ [format "%s%s" SynopsysInstall /dw/sim\_ver] \ !!your-library-path-goes-here!!] #/\* target library [ist !!your-library-name!!.db] #/\* synthetic\_library is set in .synopsys\_dc.setup to be \*/ #/\* the dw\_foundation library. \*/ set link\_library [concat [concat "\*" \$target\_library] \$synthetic\_library]

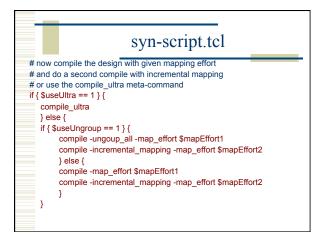

### syn-script.tcl #/\* below are parameters that you will want to set for each design \*/ #/\* list of all HDL files in the design \*/ set myFiles [list !!all-your-structur ;# verilog or VHDL set fileFormat verilog set basename!! ;# Name of top-level module set myClk !!clk!! ;# The name of your clock ;# 1 if virtual clock, 0 if real clock set virtual 0 #/\* compiler switches... \*/ set useUltra 1 ;# 1 for compile ultra, 0 for compile #mapEffort, useUngroup are for #non-ultra compile. set mapEffort1 medium ;# First pass - low, medium, or high set mapEffort2 medium high ;# second pass - low, medium, or set useUngroup 1 ;# 0 if no flatten, 1 if flatten

```

syn-script.tcl

#/* Timing and loading information */

set myPeriod ns !!10!!

;# desired clock period (sets speed goal)

set myInDelay_ns !!0.25!!

;# delay from clock to inputs valid

set myOutDelay_ns !!0.25!!

;# delay from clock to output valid

set myInputBuf !!INVX4!!

;# name of cell driving the inputs

set myLoadLibrary !!Lib!!

;# name of library the cell comes from

set myLoadPin !!A!!

;# pin that outputs drive

#/* Control the writing of result files */

set runname struct ;# Name appended to output files

```

## #/\* the following control which output files you want. They \*/ #/\* should be set to 1 if you want the file, 0 if not \*/ set write\_v1 :# compiled structural Verilog file set write\_ddc 0 ;# compiled file in ddc format set write\_sdf 0 ;# sdf file for back-annotated timing sim set write\_sdc 1 ;# sdc constraint file for place and route set write\_rep 1 :# report file from compilation set write\_pow 0 ;# report file for power estimate

```

# analyze and elaborate the files

analyze -format $fileFormat -lib WORK $myfiles

elaborate $basename -lib WORK -update

current_design $basename

# The link command makes sure that all the required design

# parts are linked together.

# The uniquify command makes unique copies of replicated modules.

link

uniquify

# now you can create clocks for the design

if {$virtual == 0 }{

create_clock -period $myPeriod_ns $myClk

} else {

create_clock -period $myPeriod_ns -name $myClk

}

```

```

syn-script.tcl

# Set the driving cell for all inputs except the clock

# The clock has infinite drive by default. This is usually

# what you want for synthesis because you will use other

# tools (like SOC Encounter) to build the clock tree (or define it by hand).

set_driving_cell -library $myLoadLibrary -lib_cell $myInputBuf \

[remove_from_collection [all_inputs] $myClk]

# set the input and output delay relative to myclk

set_input_delay $myInDelay_ns -clock $myClk \

[remove_from_collection [all_inputs] $myClk]

set output delay $myOutDelay ns -clock $myClk [all outputs]

# set the load of the circuit outputs in terms of the load

# of the next cell that they will drive, also try to fix hold time issues

set_load [load_of [format "%s%s%s%s%s" $myLoadLibrary \

"/" $myInputBuf "/" $myLoadPin]] [all_outputs]

set_fix_hold $myClk

```

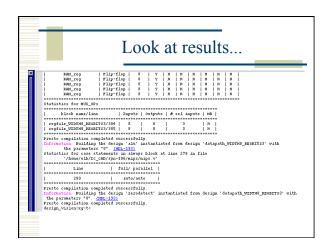

### **Using Scripts**

- Modify syn-script.tcl or write your own

- syn-dc -f scriptname.tcl

- Make sure to check output!!!!

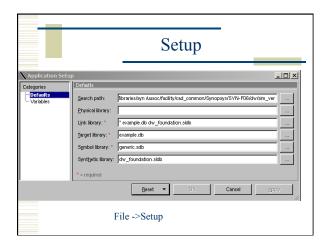

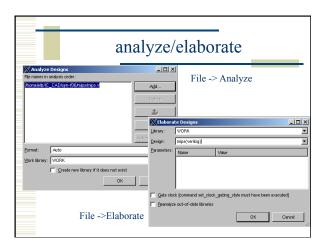

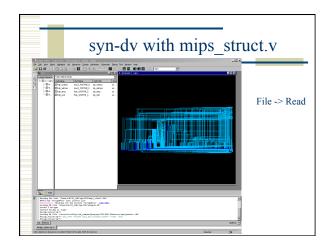

### Using Design Vision

- You can do all of these commands from the design vision gui if you like

- syn-dv

- Follow the same steps as the script

- Set libraries in your own .synopsys dc.setup

- analyze/elaborate

- define clock and set constraints

- compile

- write out results

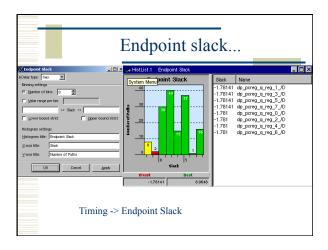

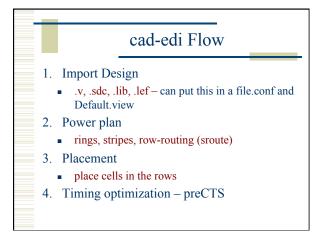

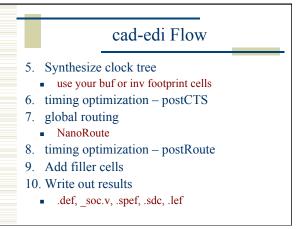

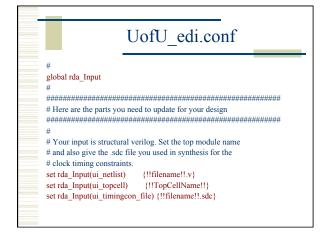

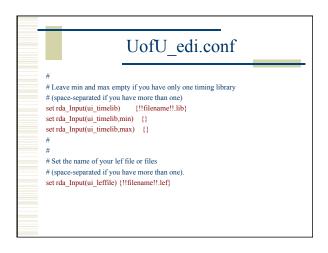

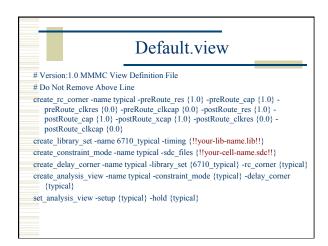

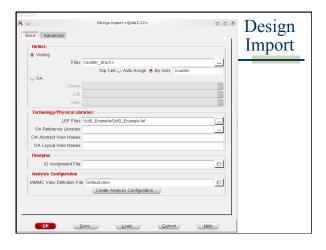

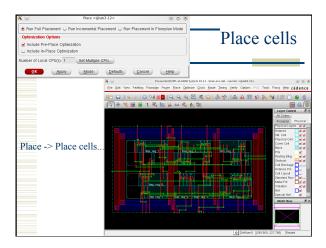

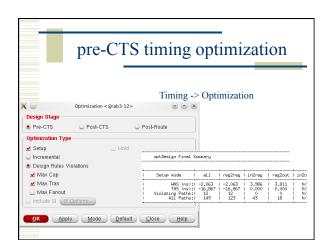

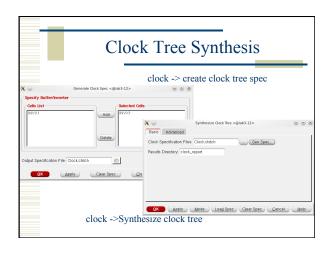

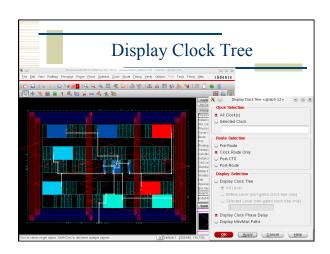

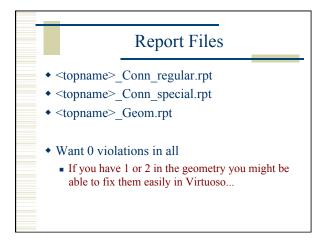

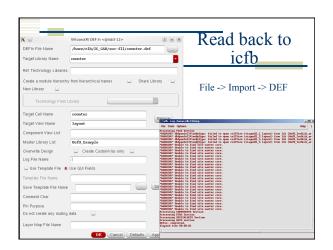

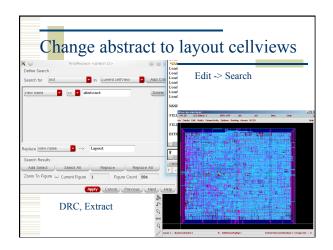

# Need structural Verilog, .sdc, library.lib, library.lef make a new dir for edi.... <design>.conf is also very helpful use UofU\_soc.conf as starting point. And Default.view Usual warnings about scripting... UofU\_edi.tcl is the generic script .../local/class/6710/F11/cadence/EDI

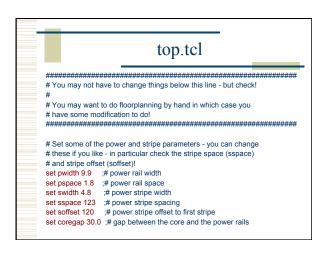

### **Encounter Scripting**

- Usual warnings know what's going on!

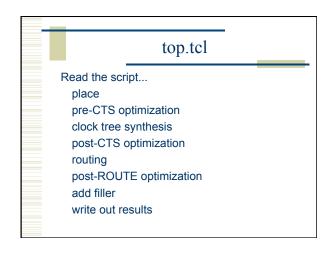

- Use top.tcl as a starting point

- And the other .tcl files it calls...

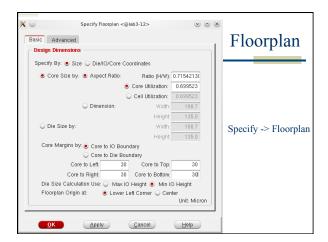

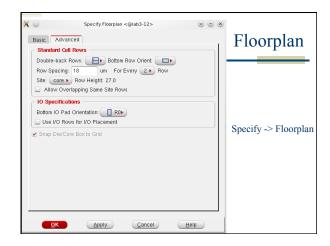

- EDI has a floorplanning stage that you may want to do by hand

- write another script to read in the floorplan and go from there...

- Use encounter.cmd to see the text versions of what you did in the GUI...

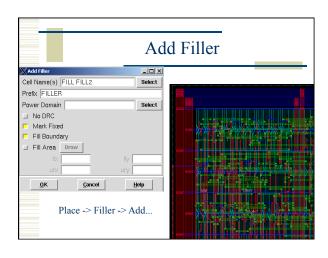

### # set the basename for the config and floorplan files. This # will also be used for the .lib, .lef, .v, and .spef files... set basename "mips" # set the name of the filler cells - you don't need a list # if you only have one set fillerCells FILL

### # These set the percent utilization target (how dense should # the cells be placed), and the gap for routing between rows. # These are good starting values for small macros. Larger or # more complex macros will likely need a lowered usepct or # larger rowgap or both. set usepct 0.65; # percent utilization in placing cells set rowgap 30; # gap between pairs of std cell rows # "aspect" sets the shape of the floorplan: less than 1.0 # is landscape, greater than 1.0 is portrait, 1.0 is square set aspect 0.60; # aspect ratio of overall cell

#set fillerCells [list FILL FILL2]

## # # Set the flag for SOC to automatically figure out buf, inv, etc. set dbgGPSAutoCellFunction 1 # Import design and floorplan # If the config file is not named \$basename.conf, edit this line. loadConfig \$basename.conf 0 commitConfig

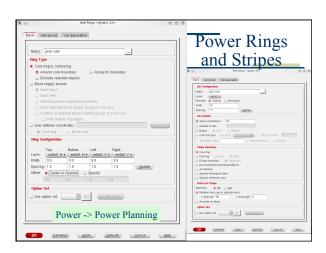

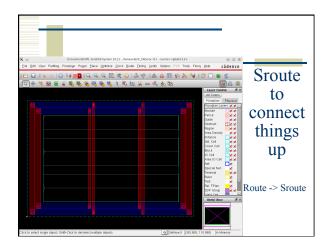

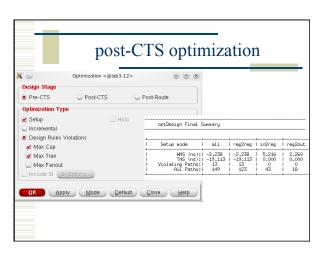

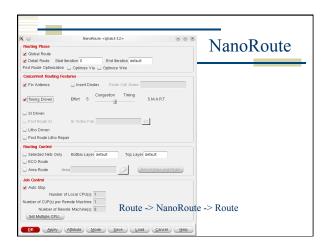

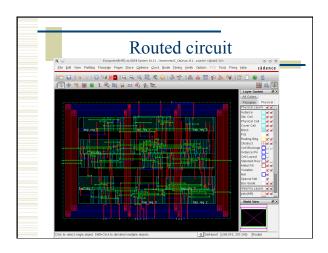

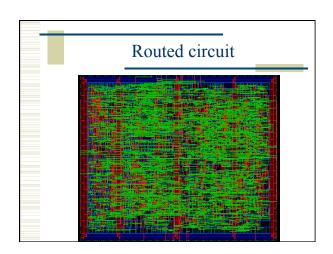

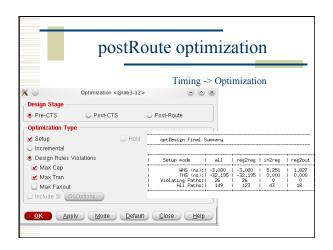

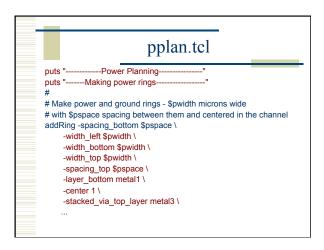

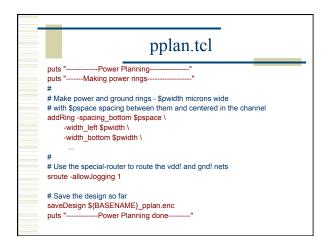

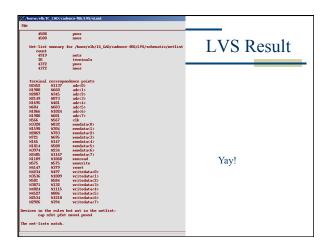

## # source the files that operate on the circuit source fplan.tcl ;# create the floorplan (might be done by hand...) source pplan.tcl ;# create the power rings and stripes source place.tcl ;# Place the cells and optimize (pre-CTS) source cts.tcl ;# Create the clock tree, and optimize (post-CTS) source route.tcl ;# Route the design using nanoRoute source verify.tcl ;# Verify the design and produce output files exit

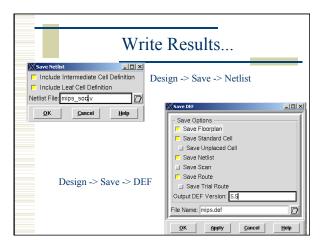

# Summary • Behavioral -> Structural -> Layout • Can be automated by scripting, but make sure you know what you're doing • on-line tutorials for TCL • Google "tcl tutorial" • Synopsys documentation for design\_compiler • encounter.cmd (and documentation) for EDI • End up with placed and routed core layout • or BLOCK for later use...