### Introduction to CMOS VLSI Design

#### Lecture 1: Circuits & Layout

**David Harris**

Harvey Mudd College Spring 2004

#### **Outline**

- □ A Brief History

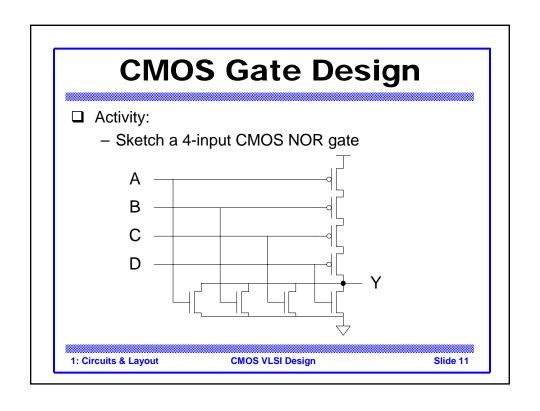

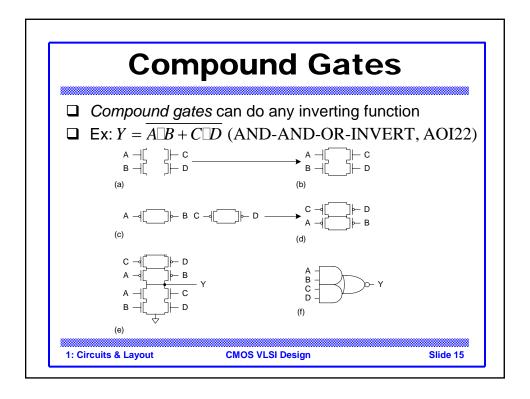

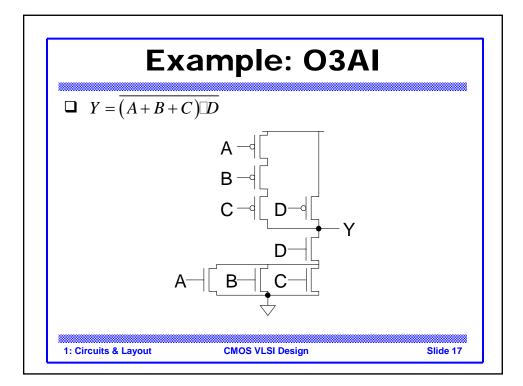

- □ CMOS Gate Design

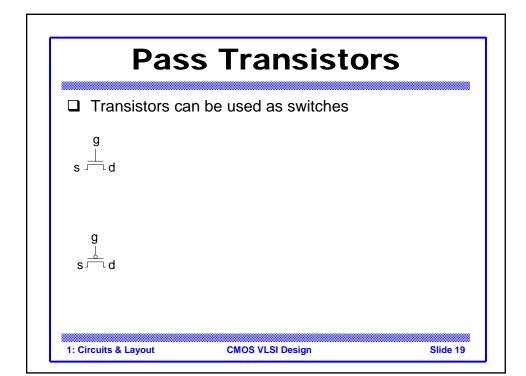

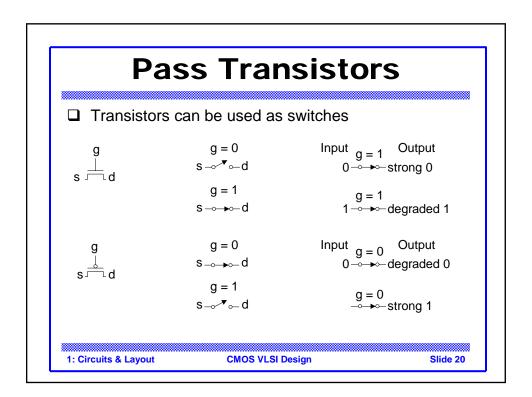

- Pass Transistors

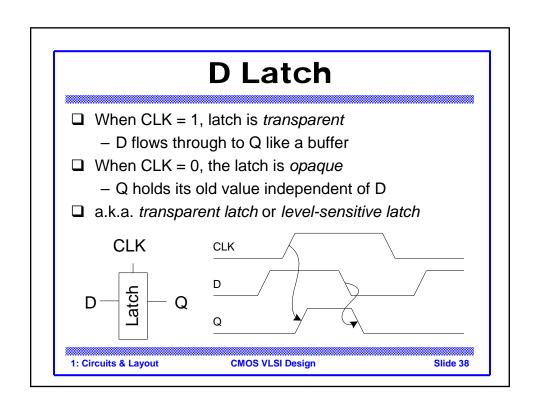

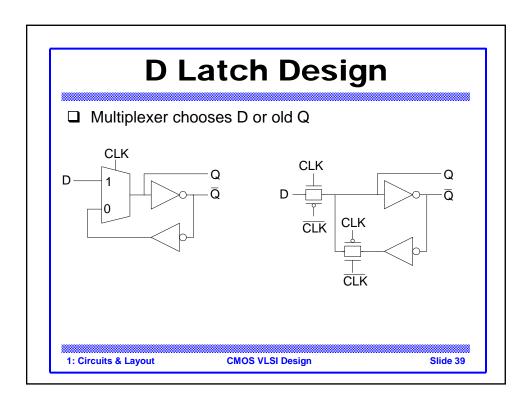

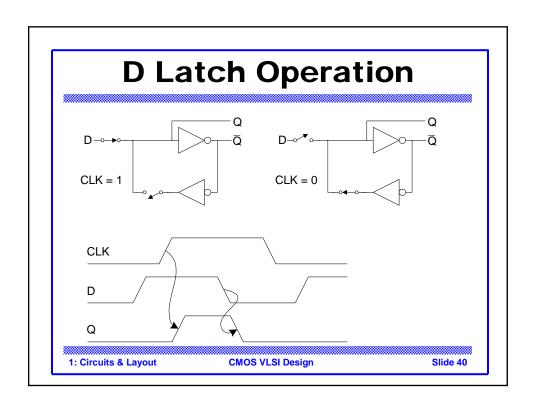

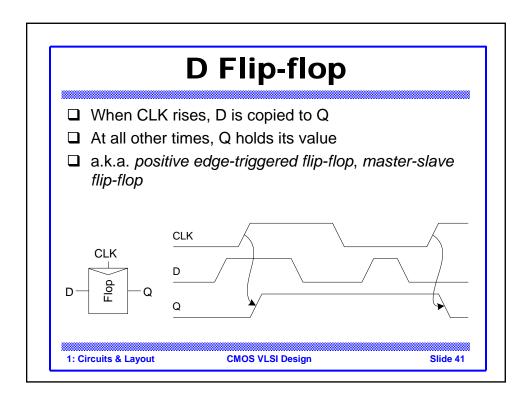

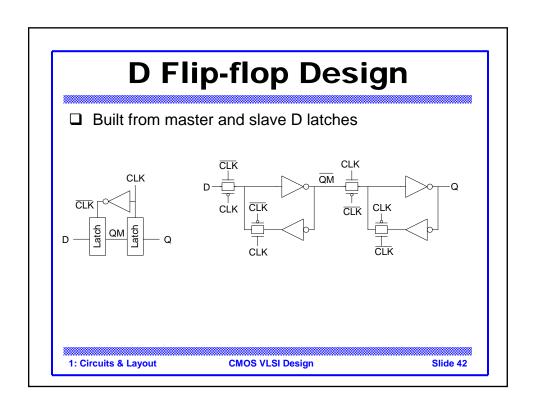

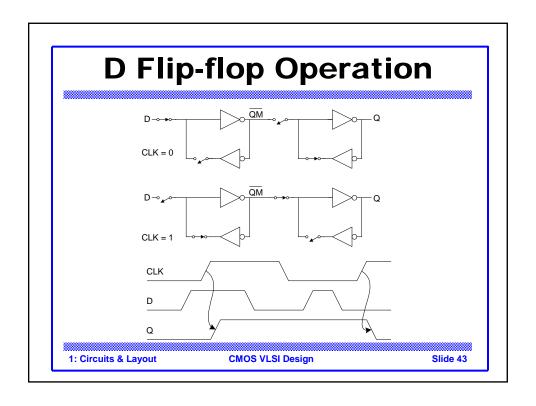

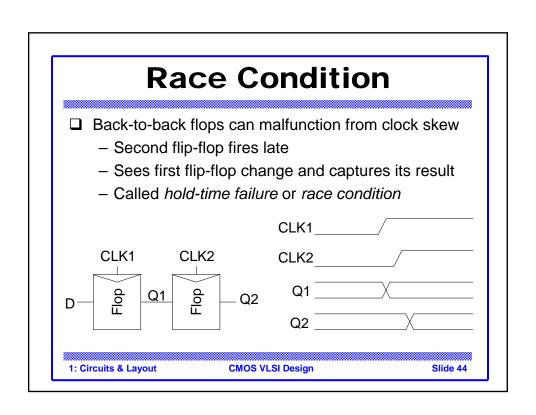

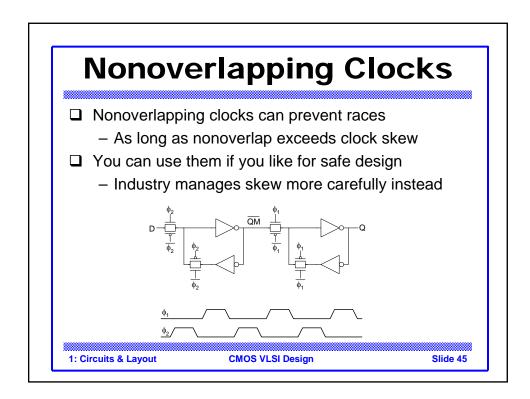

- □ CMOS Latches & Flip-Flops

- Standard Cell Layouts

- □ Stick Diagrams

1: Circuits & Layout

CMOS VLSI Design

#### **A Brief History**

- ☐ 1958: First integrated circuit

- Flip-flop using two transistors

- Built by Jack Kilby at Texas Instruments

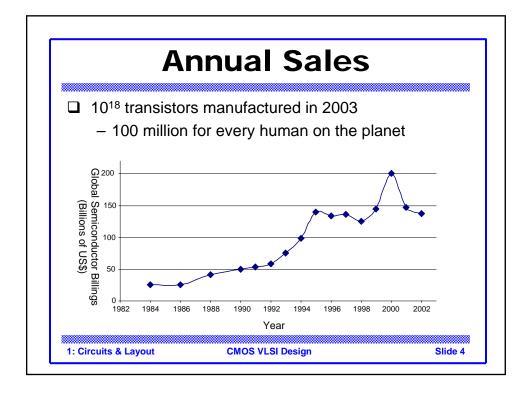

- **2**003

- Intel Pentium 4 μprocessor (55 million transistors)

- 512 Mbit DRAM (> 0.5 billion transistors)

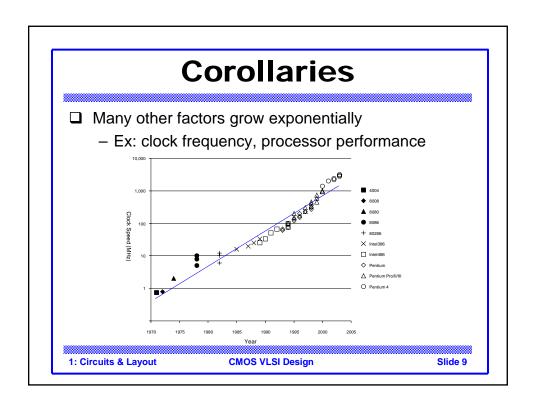

- □ 53% compound annual growth rate over 45 years

- No other technology has grown so fast so long

- Driven by miniaturization of transistors

- Smaller is cheaper, faster, lower in power!

- Revolutionary effects on society

1: Circuits & Layout

**CMOS VLSI Design**

#### Invention of the Transistor

- □ Vacuum tubes ruled in first half of 20<sup>th</sup> century Large, expensive, power-hungry, unreliable

- ☐ 1947: first point contact transistor

- John Bardeen and Walter Brattain at Bell Labs

- Read Crystal Fire

by Riordan, Hoddeson

1: Circuits & Layout

CMOS VLSI Design

Slide 5

#### **Transistor Types**

- Bipolar transistors

- npn or pnp silicon structure

- Small current into very thin base layer controls large currents between emitter and collector

- Base currents limit integration density

- Metal Oxide Semiconductor Field Effect Transistors

- nMOS and pMOS MOSFETS

- Voltage applied to insulated gate controls current between source and drain

- Low power allows very high integration

1: Circuits & Layout

**CMOS VLSI Design**

- ☐ 1970's processes usually had only nMOS transistors

- Inexpensive, but consume power while idle

Intel 1101 256-bit SRAM

Intel 4004 4-bit µProc

☐ 1980s-present: CMOS processes for low idle power

1: Circuits & Layout

**CMOS VLSI Design**

Slide

####

##

1: Circuits & Layout

**CMOS VLSI Design**

#### Signal Strength

- ☐ Strength of signal

- How close it approximates ideal voltage source

- $\Box$   $V_{DD}$  and GND rails are strongest 1 and 0

- □ nMOS pass strong 0

- But degraded or weak 1

- pMOS pass strong 1

- But degraded or weak 0

- ☐ Thus nMOS are best for pull-down network

1: Circuits & Layout

**CMOS VLSI Design**

#### **Transmission Gates**

- ☐ Pass transistors produce degraded outputs

- ☐ Transmission gates pass both 0 and 1 well

1: Circuits & Layout

CMOS VLSI Design

Slide 21

#### **Transmission Gates**

- Pass transistors produce degraded outputs

- ☐ Transmission gates pass both 0 and 1 well

$0 \longrightarrow -strc$  g = 1, gb = 0  $a \longrightarrow -b$  g = 1, gb = 0  $1 \longrightarrow -b$

g = 0, gb = 1 g = 1, gb = 0  $0 \rightarrow \infty$  strong 0

Output

1⊸→ strong 1

1: Circuits & Layout

**CMOS VLSI Design**

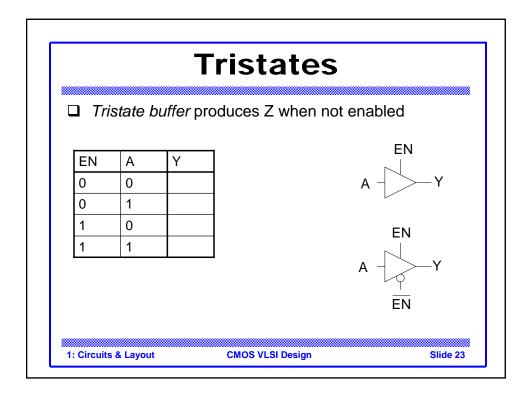

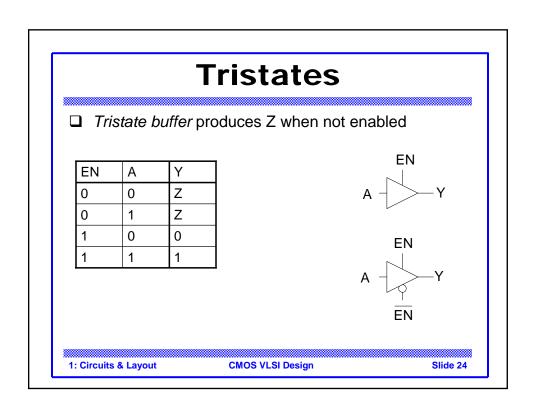

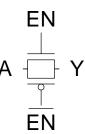

#### **Nonrestoring Tristate**

- ☐ Transmission gate acts as tristate buffer

- Only two transistors

- But nonrestoring

- Noise on A is passed on to Y

1: Circuits & Layout

CMOS VLSI Design

Slide 25

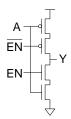

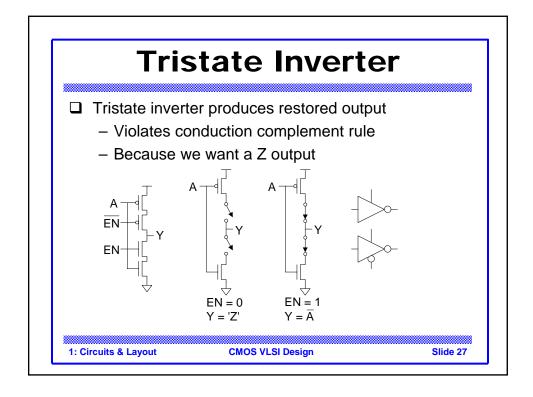

#### **Tristate Inverter**

- ☐ Tristate inverter produces restored output

- Violates conduction complement rule

- Because we want a Z output

1: Circuits & Layout

**CMOS VLSI Design**

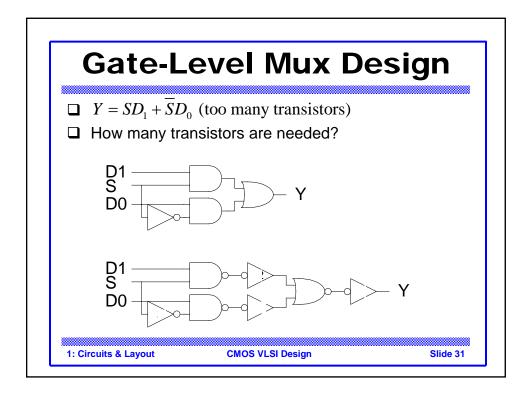

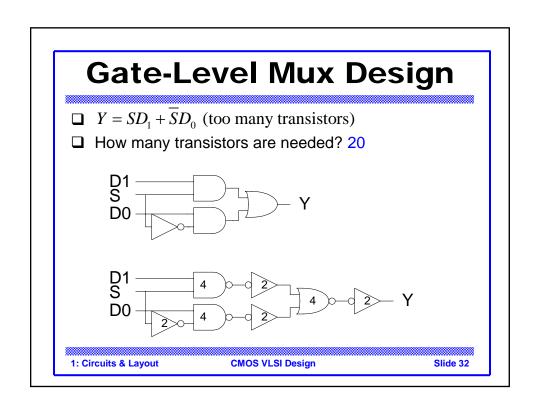

# Gate-Level Mux Design $Y = SD_1 + \overline{S}D_0 \text{ (too many transistors)}$ How many transistors are needed?

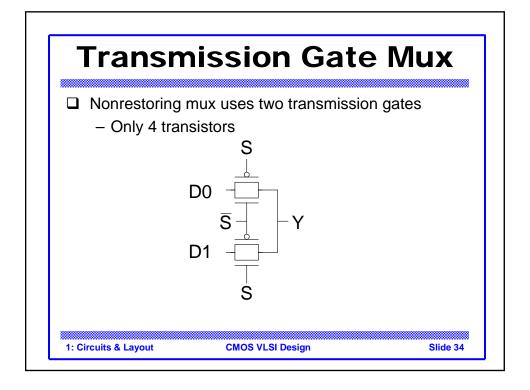

# Transmission Gate Mux ☐ Nonrestoring mux uses two transmission gates

1: Circuits & Layout

CMOS VLSI Design

####

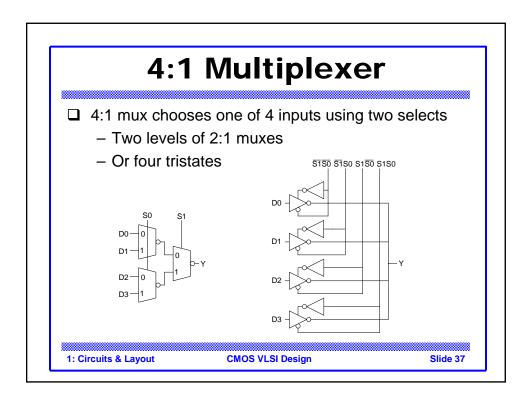

#### 4:1 Multiplexer

☐ 4:1 mux chooses one of 4 inputs using two selects

1: Circuits & Layout

CMOS VLSI Design