### Verilog Synthesis Examples

CS/EE 3710 Fall 2010

Mostly from CMOS VLSI Design by Weste and Harris

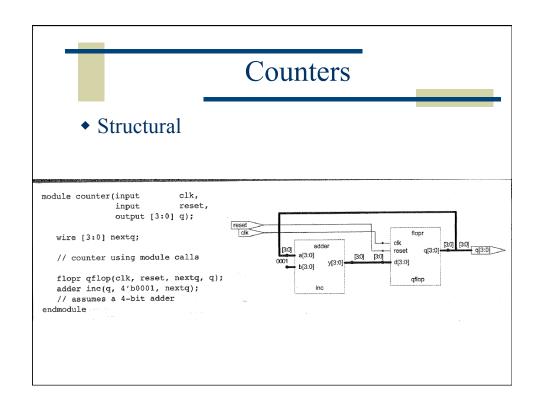

- Using continuous assignments

- ISE can build you a nice adder

- Easier than specifying your own

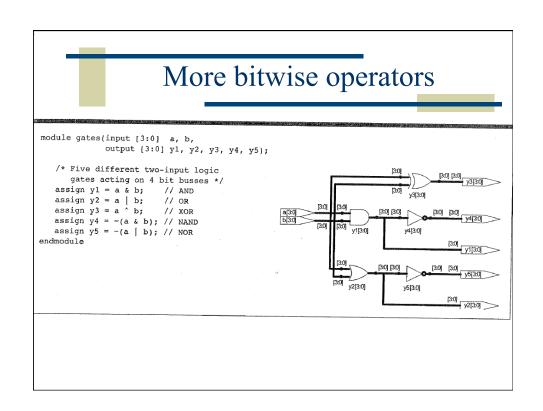

### **Bitwise Operators**

• Bitwise operations act on vectors (buses)

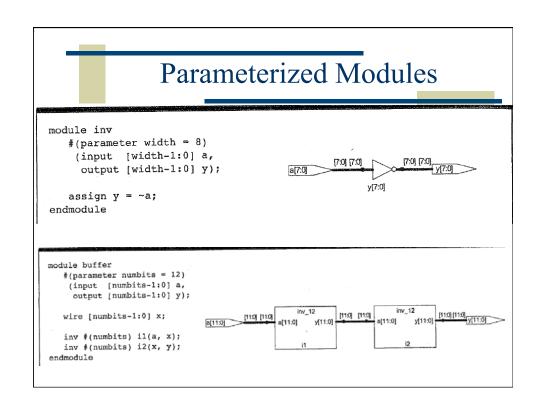

```

module inv(input [3:0] a, output [3:0] y);

assign y = ~a;

endmodule

```

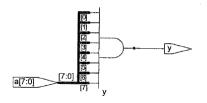

### **Reduction Operators**

- Apply operator to a single vector

- Reduce to a single bit answer

endmodule

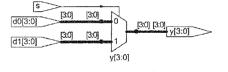

## **Conditional Operator**

- Classic mux

- Can be confusing if you get crazy

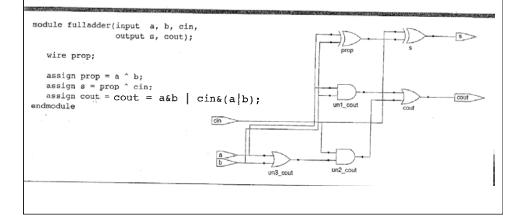

Internal wires and regs can be used inside a module

```

module fulladder(input a, b, cin, output s, cout);

wire prop;

assign prop = a ^ b;

assign cout = (a & b) | (cin & (a | b));

endmodule

cin

un3_cout

un2_cout

```

### Using internal signals

Internal wires and regs can be used inside a module

## **Operator Precedence**

| Table A.1 Operator Precedence |                             |            |  |  |

|-------------------------------|-----------------------------|------------|--|--|

| Symbol                        | Meaning                     | Precedence |  |  |

| -                             | NOT                         | Highest    |  |  |

| *, /, %                       | MUL, DIV, MODULO            |            |  |  |

| +, -                          | PLUS, MINUS                 |            |  |  |

| <<,>>,                        | Logical Left/Right Shift    |            |  |  |

| <<<, >>>                      | Arithmetic Left/Right Shift |            |  |  |

| <, <=, >, >=                  | Relative Comparison         |            |  |  |

| ==, !=                        | Equality Comparison         |            |  |  |

| &, ~&                         | AND, NAND                   |            |  |  |

| ^, ~^                         | XOR, XNOR                   |            |  |  |

| 1, ~1                         | OR, NOR                     |            |  |  |

| ?:                            | Conditional                 |            |  |  |

### Constants

- Specified in binary, octal, decimal, or hex

- Note use of underscore in long binary numbers

| Table A.2 Constants |         |             |                    |              |  |

|---------------------|---------|-------------|--------------------|--------------|--|

| Number              | # Bits  | Base        | Decimal Equivalent | Stored       |  |

| 3'b101              | 3       | Binary      | 5                  | 101          |  |

| 'b11                | unsized | Binary      | 3                  | 00000000011  |  |

| 8'b11               | 8       | Binary      | 3                  | 00000011     |  |

| 8'b1010_1011        | 8       | Binary      | 171                | 10101011     |  |

| 3'd6                | 3       | Decimal     | 6                  | 110          |  |

| 6'042               | 6       | Octal       | 34                 | 100010       |  |

| 8'hAB               | 8       | Hexadecimal | 171                | 10101011     |  |

| 42                  | unsized | Decimal     | 42                 | 000000101010 |  |

# Tristates • Assign the value z • Just say NO! • No on-board tri-states on Spartan3e FPGAs • Use MUXs instead! module tristate(input [3:0] a, input en, output [3:0] y); assign y = en ? a : 4'bz; endmodule

### Bit Swizzling

- Sometimes useful to work on part of a bus, or combine different signals together

- Use bus (vector) notation

### Bit Swizzling

- Sometimes useful to work on part of a bus, or combine different signals together

- Use concatenation {} operator

```

module mul(input [7:0] a, b, output [7:0] upper, lower);

assign {upper, lower} = a*b;

endmodule

module mul(input [7:0] a, b, output [7:0] upper, lower);

assign {upper, lower} = a*b;

endmodule

```

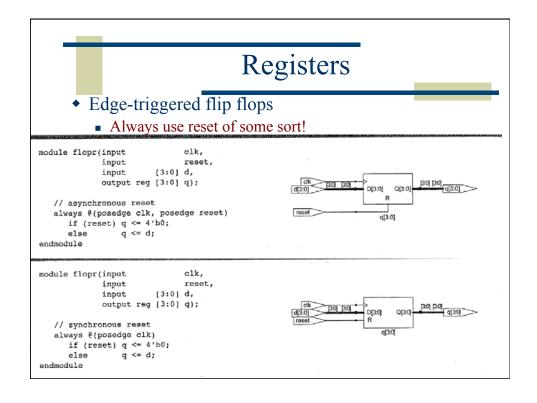

# Registers

- Can also add an enable signal

- Only capture new data on clock and en

```

module flopren(input

clk,

input

reset,

input

en,

[3:0] d,

input

[3:0] q[3:0]

D[3:0] Q[3:0]

output reg [3:0] q);

// asynchronous reset

always @(posedge clk, posedge reset)

q[3:0]

if (reset) q <= 4'b0;

else if (en) q <= d;

endmodule

```

### Comb Logic with Always blocks

- Always blocks are often sequential

- But, if you have all RHS variables in the sensitivity list it can be combinational

- Remember that you still must assign to a reg

## Comb Logic with Always blocks

- Always blocks are often sequential

- But, if you have all RHS variables in the sensitivity list it can be combinational

- Remember that you still must assign to a reg

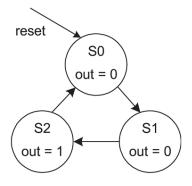

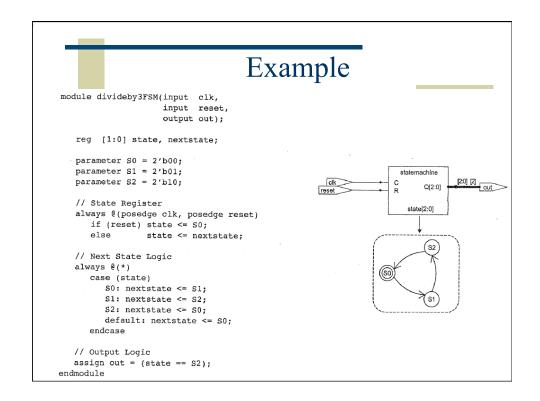

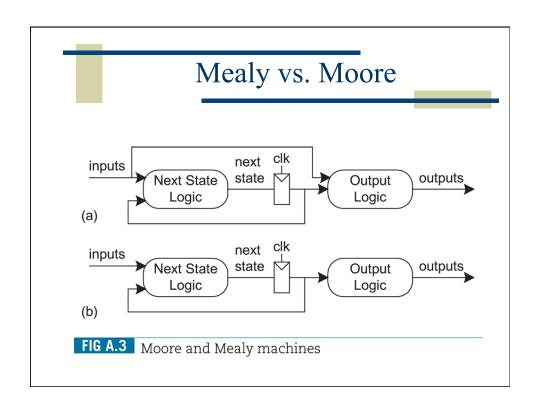

### Finite State Machines

- Divide into three sections

- State register

- Next state logic

- output logic

- Use parameters for state encodings

# Example no inputs, one output, to

Three states, no inputs, one output, two state bits

FIG A.4 Divide-by-3 counter state transition diagram

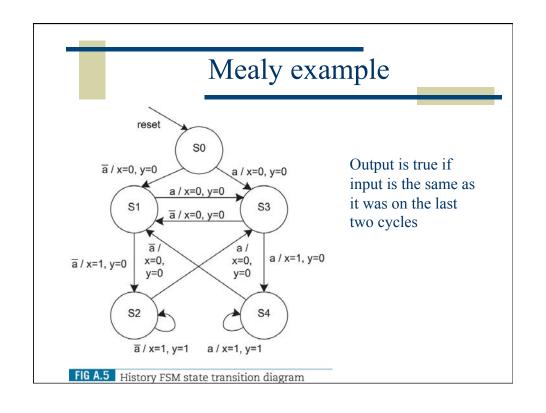

### Mealy Example module historyFSM(input clk, input reset, input a, // Next State Logic output x, y); always @(\*) case (state) reg [2:0] state, nextstate; S0: if (a) nextstate <= S3; else nextstate <= S1; parameter S0 = 3'b000; S1: if (a) nextstate <= S3; parameter S1 = 3'b010; else nextstate <= S2; parameter S2 = 3'b011; S2: if (a) nextstate <= S3; parameter S3 = 3'b100; else nextstate <= S2; parameter S4 = 3'b101; S3: if (a) nextstate <= S4; else nextstate <= S1; // State Register S4: if (a) nextstate <= S4; always @(posedge clk, posedge reset) else nextstate <= \$1; if (reset) state <= S0; default: nextstate <= S0; state <= nextstate; endcase // Output Logic assign x = (state[1] & ~a)(state[2] & a); assign y = (state[1] & state[0] & ~a)(state[2] & state[0] & a);

endmodule

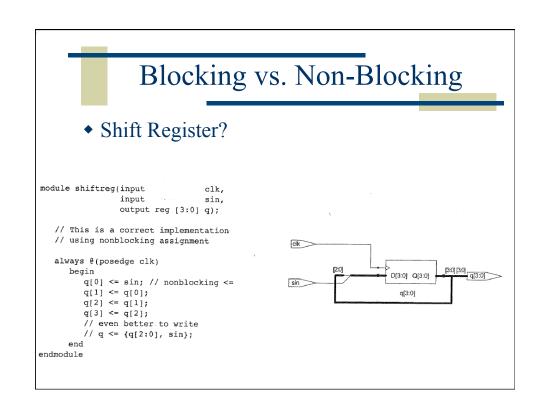

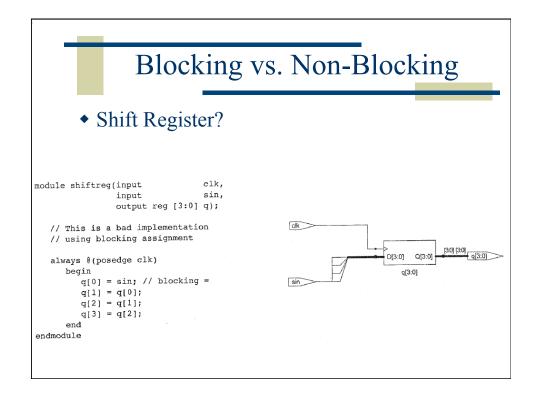

- Use only non-blocking assignments in always blocks

- Define combinational logic using assign statements whenever practical

- Unless if or case makes things more readable

- When modeling combinational logic with always blocks, if a signal is assigned in one branch of an if or case, it needs to be assigned in all branches

### Verilog Style Guide

- Include default statements in your case statements

- Use parameters to define state names and constants

- Properly indent your code

- Use comments liberally

- Use meaningful variable names

- Do NOT ignore synthesis warnings unless you know what they mean!

- Be very careful if you use both edges of the clock

- It's much safer to stick with one

- I.e. @(posedge clock) only

- Be certain not to imply latches

- Watch for synthesis warnings about implied latches

- Provide a reset on all registers

### Verilog Style Guide

- Provide a common clock to all registers

- Avoid gated clocks

- Use enables instead