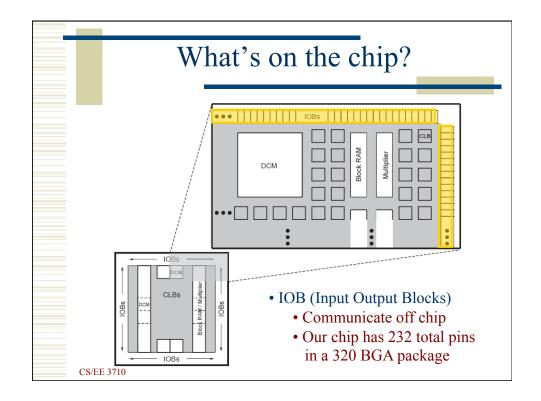

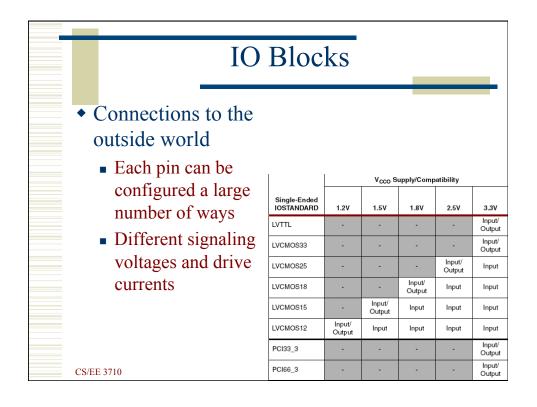

|                                 |              |                       |                    |                   |                       |                            | IO   | Bloc     | ks     |        |                  |                  |                 |

|---------------------------------|--------------|-----------------------|--------------------|-------------------|-----------------------|----------------------------|------|----------|--------|--------|------------------|------------------|-----------------|

| •                               | οι           | itsi<br>Ea<br>co      | de<br>ch j<br>nfig | wo<br>oin<br>gure | rld<br>can<br>d a     | larg                       | -    | NO       | OTE    | e! N   | 0 5V             | •                |                 |

| number of ways Different signal |              |                       |                    | 2                 | g                     | Single-Ended<br>IOSTANDARD | 1.2V | 1.5V     | 1.8V   | 2.5V   | 3.3V             |                  |                 |

| voltages and drive<br>currents  |              |                       |                    |                   |                       | LVTTL                      | -    | -        | -      | -      | Input/<br>Output |                  |                 |

|                                 |              |                       |                    |                   |                       | LVCMOS33                   |      |          |        |        | Input/<br>Outpu  |                  |                 |

|                                 |              | Outou                 | t Drive            | Curre             | nt (mA                | )                          |      | LVCMOS25 |        |        |                  | Input/<br>Output | Input           |

| IOSTANDARD                      | 2            | 4                     | 6                  | 8                 | 12                    | ,<br>16                    |      | LVCMOS18 | -      | -      | Input/<br>Output | Input            | Input           |

| LVTTL                           | ~            | ~                     | ~                  | ~                 | ✓                     | ✓                          |      | LVCMOS15 |        | Input/ | Input            | Input            | Input           |

| LVCMOS33                        | ✓            | <ul> <li>✓</li> </ul> | $\checkmark$       | $\checkmark$      | <ul> <li>✓</li> </ul> | ~                          |      |          | Input/ | Output |                  |                  |                 |

| VCMOS25                         | $\checkmark$ | $\checkmark$          | ✓<br>✓             | ✓<br>✓            | <ul> <li>✓</li> </ul> | -                          |      | LVCMOS12 | Output | Input  | Input            | Input            | Input           |

|                                 | ▼<br>✓       | ▼<br>✓                | ▼<br>✓             | v                 | -                     | -                          |      | PCI33_3  |        |        | •                |                  | Input/<br>Outpu |

| LVCMOS15                        |              |                       |                    |                   |                       |                            |      | PCI66 3  |        | -      | -                |                  | Input/<br>Outpu |

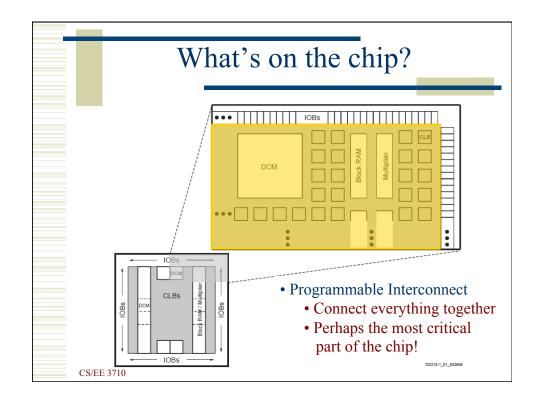

| Interconn                                 | lect                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vork                                      |                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Switch<br>Matrix IOB Switch<br>Matrix IOB | Switch<br>Matrix IOB Switch<br>Matrix                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Switch<br>Matrix CLB Switch<br>Matrix CLB | Switch<br>Matrix CLB Switch<br>Matrix                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Switch Arrive CLB Switch Arrive CLB       | Switch<br>Matrix CLB Switch<br>Matrix                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Switch CLB Switch Atrix CLB               | Switch<br>Matrix CLB Switch<br>Matrix                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Switch CLB Switch CLB                     | Switch<br>Matrix CLB Switch<br>Matrix                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                           | ct to 'switch matrix' w<br>vork<br>matrix interconnects<br>Switch + 10B<br>Switch + CLB<br>Switch + CLB | Switch       IOB       Switch       IOB       Switch         Matrix       IOB       Switch       IOB       Switch         Switch       IOB       Switch       IOB       Switch         Matrix       IOB       Switch       IOB       Switch         Switch       IOB       Switch       IOB       Switch         Matrix       IOB       Switch       IOB       Switch         Switch       IOB       Switch |

| Four types<br>of wires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                                                                                      |              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------|--------------|

| Four types       Image: CLB image: CL |           |                                                                                      | Interconnect |

| (horizontal channel<br>shown as an example)<br>Horizontal and<br>Vertical Double Lines<br>(horizontal channel<br>shown as an example)<br>Direct Connections<br>CLB CLB CLB CLB CLB CLB CLB CLB<br>USUBLING<br>(brizontal channel<br>shown as an example)<br>CLB CLB CLB CLB CLB CLB<br>CLB CLB CLB CLB CLB<br>CLB CLB CLB CLB CLB CLB<br>CLB CLB CLB CLB CLB CLB<br>CLB CLB CLB CLB CLB CLB CLB CLB CLB<br>CLB CLB CLB CLB CLB CLB CLB CLB CLB CLB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | Vertical Long Lines<br>(horizontal channel<br>shown as an example)<br>Horizontal and |              |

| Vertical Double Lines<br>(horizontal channel<br>shown as an example)<br>Direct Connections<br>CLB CLB CLB<br>CLB CLB<br>CLB CLB<br>CLB<br>CLB<br>CLB<br>CLB<br>CLB<br>CLB<br>CLB<br>CLB<br>CLB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | orwnes    | (horizontal channel<br>shown as an example)                                          |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | (horizontal channel<br>shown as an example)                                          |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | Direct Connections                                                                   |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CS/EE 271 |                                                                                      |              |

|           |                 |                              |           | Spa                         | arta                                | an                      | XC3                                    | BE5                                 | 5005                     | 5    |                     |                                      |

|-----------|-----------------|------------------------------|-----------|-----------------------------|-------------------------------------|-------------------------|----------------------------------------|-------------------------------------|--------------------------|------|---------------------|--------------------------------------|

|           |                 |                              |           |                             |                                     |                         |                                        |                                     |                          |      |                     |                                      |

|           |                 |                              |           |                             |                                     |                         |                                        |                                     |                          |      |                     |                                      |

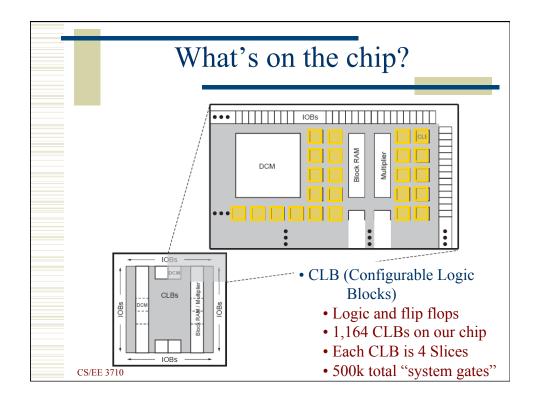

| Device    | System<br>Gates | Equivalent<br>Logic<br>Cells | (<br>Rows | CLB<br>One CLB =<br>Columns | Array<br>Four Slid<br>Total<br>CLBs | ces)<br>Total<br>Slices | Distributed<br>RAM bits <sup>(1)</sup> | Block<br>RAM<br>bits <sup>(1)</sup> | Dedicated<br>Multipliers | DCMs | Maximum<br>User I/O | Maximum<br>Differential<br>I/O Pairs |

| XC3S100E  | 100K            | 2,160                        | 22        | 16                          | 240                                 | 960                     | 15K                                    | 72K                                 | 4                        | 2    | 108                 | 40                                   |

| XC3S250E  | 250K            | 5,508                        | 34        | 26                          | 612                                 | 2,448                   | 38K                                    | 216K                                | 12                       | 4    | 172                 | 68                                   |

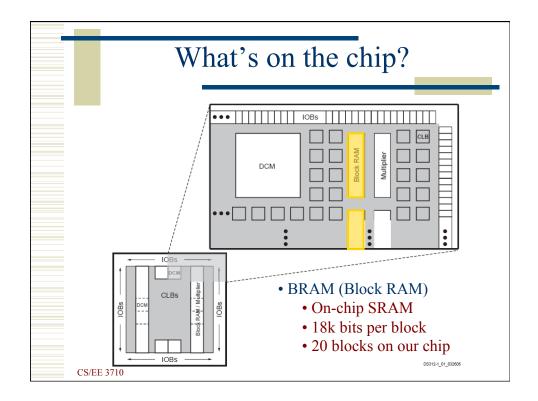

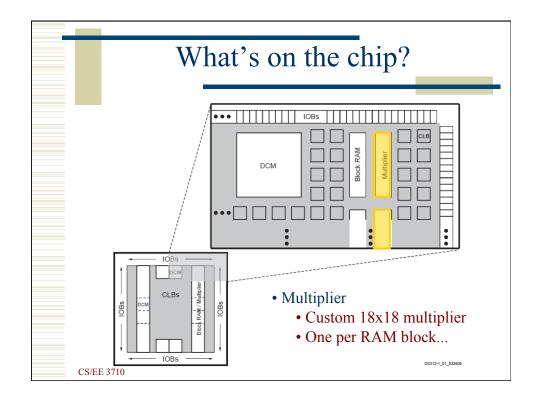

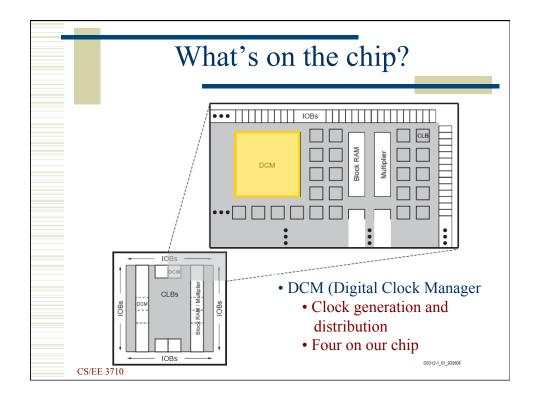

| XC3S500E  | 500K            | 10,476                       | 46        | 34                          | 1,164                               | 4,656                   | 73K                                    | 360K                                | 20                       | 4    | 232                 | 92                                   |

| XC3S1200E | 1200K           | 19,512                       | 60        | 46                          | 2,168                               | 8,672                   | 136K                                   | 504K                                | 28                       | 8    | 304                 | 124                                  |

| XC3S1600E | 1600K           | 33,192                       | 76        | 58                          | 3,688                               | 14,752                  | 231K                                   | 648K                                | 36                       | 8    | 376                 | 156                                  |

|           |                 |                              |           |                             |                                     |                         |                                        |                                     |                          |      |                     |                                      |

|           | CS/EE 3         | 710                          |           |                             |                                     |                         |                                        |                                     |                          |      |                     |                                      |

| Structural Template                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>// RANB16_59_39 : In order to incorporate this function into the design,<br/>// Verilog : the following instance declaration needs to be placed<br/>// instance : in the body of the design code. The instance name<br/>// declaration : (RAMB16_59_59_inst) and/or the port declarations within the<br/>// code : parenthesis may be changed to properly reference and<br/>// : connect this function to the design. All inputs<br/>// : and outputs must be connected.</pre>                                                       |

| // <cut below="" code="" line="" this=""></cut>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| // RAMB16_S9_S9: Virtex-II/II-Pro, Spartan-3/3E 2k x 8 + 1 Parity bit Dual-Port RAM<br>// Xilinx HDL Language Template, version 10.1.3                                                                                                                                                                                                                                                                                                                                                                                                    |

| RAMB16 S9 S9 #(<br>.INIT_A(9'h000), // Value of output RAM registers on Port A at startup<br>.INIT_B(9'h000), // Value of output RAM registers on Port B at startup<br>.SRVAL_A(9'h000), // Port A output value upon SSR assertion<br>.SRVAL_B(9'h000), // Port B output value upon SSR assertion<br>.URITE_MODE_A("UMPITE_FIRST"), // WRITE_FIRST, READ_FIRST or NO_CHANGE<br>.URITE_MODE_A("UMPITE_FIRST"), // WRITE_FIRST, READ_FIRST or NO_CHANGE<br>.SIM_COLLISION_CHECK("ALL"), // "NONE", "WARNING_ONLY", "GENERATE_X_ONLY", "ALL" |

| <pre>// The following INIT_xx declarations specify the initial contents of the RAM // Address 0 to 511</pre>                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CS/EE 3710                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| // The next set of INITP_xx are for the parity bits<br>// Address 0 to 511<br>INITP_00(256+hoodooocococococococococococococococococ |

|-------------------------------------------------------------------------------------------------------------------------------------|

| <pre>// Address 0 to 511</pre>                                                                                                      |

| <pre>// Address 0 to 511</pre>                                                                                                      |

| <pre>// Address 0 to 511</pre>                                                                                                      |

| .INITP_00(256'h000000000000000000000000000000000000                                                                                 |

| .INITE_01(256'haoooooooooooooooooooooooooooooooooooo                                                                                |

| .NITF_02(256+haocococococococococococococococococococ                                                                               |

| .INITE_03(256'h000000000000000000000000000000000000                                                                                 |

| // Address 1024 to 1535                                                                                                             |

|                                                                                                                                     |

| ,INITE 04(256'N000000000000000000000000000000000000                                                                                 |

| .INITP 05(256'h000000000000000000000000000000000000                                                                                 |

| .N/1/                                                                                                                               |

| . INITE 06(256'h000000000000000000000000000000000000                                                                                |

| . INITP 07 (256' h000000000000000000000000000000000000                                                                              |

| AMB16 $\overline{s}$ 9 S9 inst (                                                                                                    |

| .DOA(DOA), // Port A 8-bit Data Output                                                                                              |

| .DOB(DOB), // Port B 8-bit Data Output<br>.DOPA(DOPA), // Port A 1-bit Parity Output                                                |

|                                                                                                                                     |

| .DOPB(DOPB), // Port B 1-bit Parity Output                                                                                          |

| .ADDRA(ADDRA), // Port & 11-bit Address Input<br>.ADDRB(ADDRB), // Port B 11-bit Address Input                                      |

| .CLKA(CLKA), // Port & Clock                                                                                                        |

| CLKB(CLKB), // Port B Clock                                                                                                         |

| DIA(DIA), // Port A 8-bit Data Input                                                                                                |

| .DIB(DIB), // Port B 8-bit Data Input                                                                                               |

| .DIPA(DIPA), // Port A 1-bit parity Input                                                                                           |

| <br>.DIPB(DIPB), // Port-B 1-bit parity Input                                                                                       |

| .ENA(ENA), // Port & RAM Enable Input                                                                                               |

| ENB(ENB), // Port B RAM Enable Input                                                                                                |

| .SSRA(SSRA), // Port A Synchronous Set/Reset Input                                                                                  |

| .SSRB(SSRB), // Port B Synchronous Set/Reset Input<br>.WEA(WEA), // Port A Write Enable Input                                       |

| .WLA(WLA), // FULL A WIILE ENABLE INPUL                                                                                             |

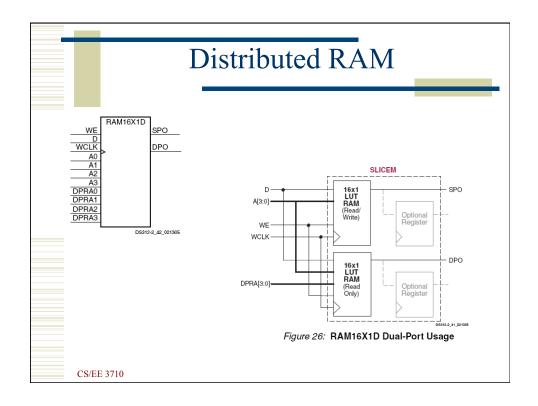

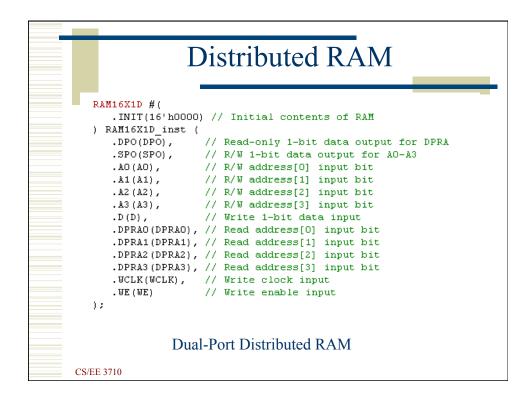

| Tal                        | ble 6-4: S | ingle-Po                    | I<br>rt and Dual-F    |                            |                        | uted RA                       | M         |

|----------------------------|------------|-----------------------------|-----------------------|----------------------------|------------------------|-------------------------------|-----------|

| Primitive                  |            | RAM Size<br>(Depth x Width) |                       | Гуре                       | Address Inputs         |                               |           |

|                            | RAM16X1S   |                             | 16 x 1                | Sing                       | gle-port               | A3, A2, A1, A0                |           |

| RAM32X1S                   |            | 32 x 1                      | Sing                  | gle-port                   | A4, A3, A2, A1, A0     |                               |           |

| RAM64X1S                   |            | 64 x 1                      | Sing                  | gle-port                   | A5, A4, A3, A2, A1, A0 |                               |           |

|                            | RAM16X1D   |                             | 16 x 1                | Du                         | al-port                | A3, A2, A1, A0                |           |

|                            | ual-Port R | AM Fund                     |                       |                            | and DPR                | A[#:0] signals are address bu | D SPO     |

| Inputs<br>WE (mode) WCLK D |            | Outputs<br>SPO DPC          |                       | A[#:0]                     | _                      | R/W Port                      |           |

|                            | X          | X                           | data_a                | data d                     |                        |                               |           |

| , ,                        |            |                             | uata_d                | uata_d                     | 1                      |                               | DPO       |

| 0 (read)                   |            | x                           | data a                | data d                     | 1                      |                               |           |

| 0 (read)<br>1 (read)       | 0<br>1     | X                           | data_a<br>data a      | data_d<br>data_d           | -                      |                               | DPRA[#:0] |

| 0 (read)                   | 0          |                             | data_a<br>data_a<br>D | data_d<br>data_d<br>data_d |                        |                               |           |

| Distributed RAM                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                    |

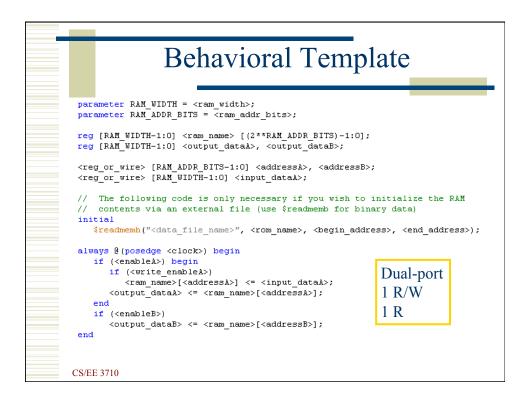

| <pre>parameter RAM_WIDTH = <ram_width>; parameter RAM_ADDR_BITS = <ram_addr_bits>;</ram_addr_bits></ram_width></pre>                                                                               |

| <pre>reg [RAM_WIDTH-1:0] <ram_name> [(2**RAM_ADDR_BITS)-1:0];</ram_name></pre>                                                                                                                     |

| <pre>wire [RAM_WIDTH-1:0] <output_data>;</output_data></pre>                                                                                                                                       |

| <reg_or_wire> [R&amp;M_ADDR_BITS-1:0] <read_address>, <write_address>;<br/><reg_or_wire> [R&amp;M_WIDTH-1:0] <input_data>;</input_data></reg_or_wire></write_address></read_address></reg_or_wire> |

| <pre>always @(posedge <clock>) if (<write_enable>)      <ram_name>[<write_address>] &lt;= <input_data>;</input_data></write_address></ram_name></write_enable></clock></pre>                       |

| <pre>assign <output_data> = <ram_name>[<read_address>];</read_address></ram_name></output_data></pre>                                                                                              |

|                                                                                                                                                                                                    |

| Dual-Port Distributed RAM                                                                                                                                                                          |

| CS/EE 3710                                                                                                                                                                                         |

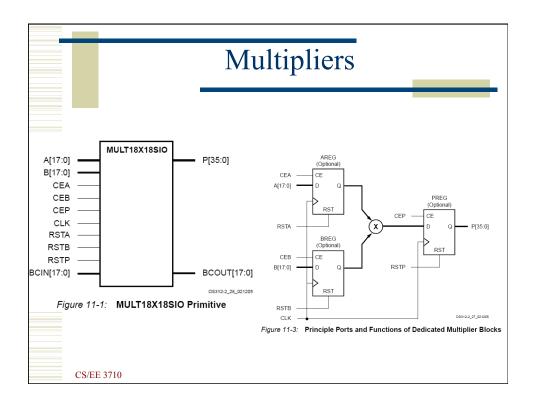

| Multipliers                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>module mult18x18sio(a,b,clk,prod);<br/>input [7:0] a;<br/>input [7:0] b;<br/>input clk;<br/>output [15:0] prod;<br/>reg [15:0] prod;<br/>always @(posedge clk) prod &lt;= a*b;<br/>endmodule</pre> |

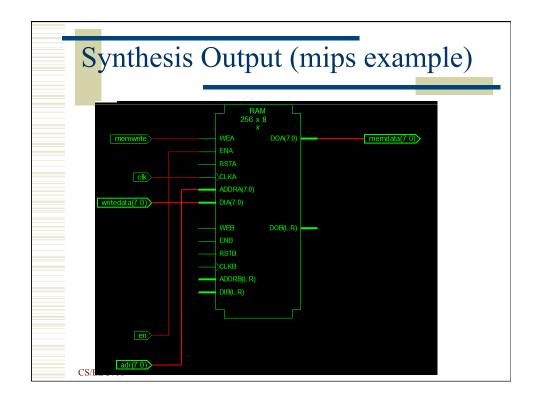

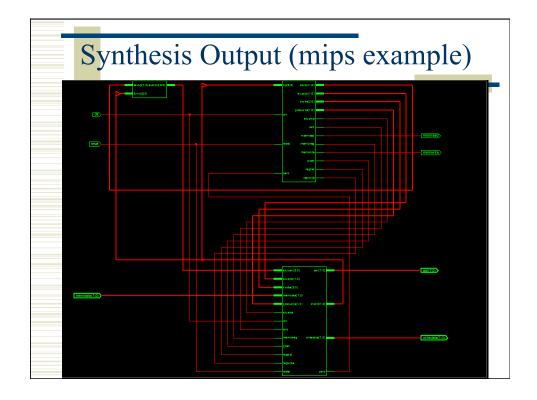

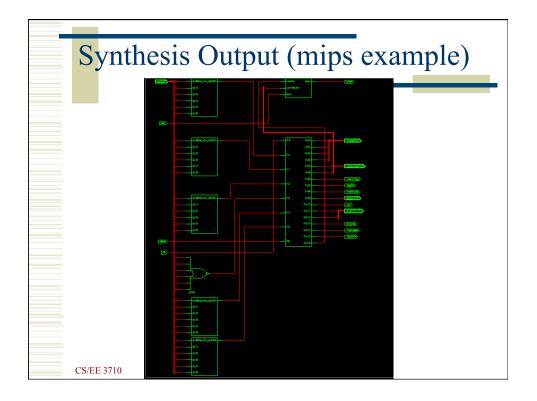

| Synthesis O                                    | utput (1               | nips exa  | mple)       |  |  |

|------------------------------------------------|------------------------|-----------|-------------|--|--|

| Di                                             | evice Utilization Summ | nary      |             |  |  |

| Logic Utilization                              | Used                   | Available | Utilization |  |  |

| Number of Slice Flip Flops                     | 79                     | 9,312     | 1%          |  |  |

| Number of 4 input LUTs                         | 193                    | 9,312     | 2%          |  |  |

| Logic Distribution                             |                        |           |             |  |  |

| Number of occupied Slices                      | 123                    | 4,656     | 2%          |  |  |

| Number of Slices containing only related logic | 123                    | 123       | 100%        |  |  |

| Number of Slices containing unrelated logic    | 0                      | 123       | 0%          |  |  |

| Total Number of 4 input LUTs                   | 193                    | 9,312     | 2%          |  |  |

| Number used as logic                           | 161                    |           |             |  |  |

| Number used for Dual Port RAMs                 | 32                     |           |             |  |  |

| Number of bonded IOBs                          | '                      | '         |             |  |  |

| Number of bonded                               | 19                     | 232       | 8%          |  |  |

| Number of RAMB16s                              | 1                      | 20        | 5%          |  |  |

| Number of BUFGMUXs                             | 1                      | 24        | 4%          |  |  |

| CS/EE 3710                                     |                        |           |             |  |  |

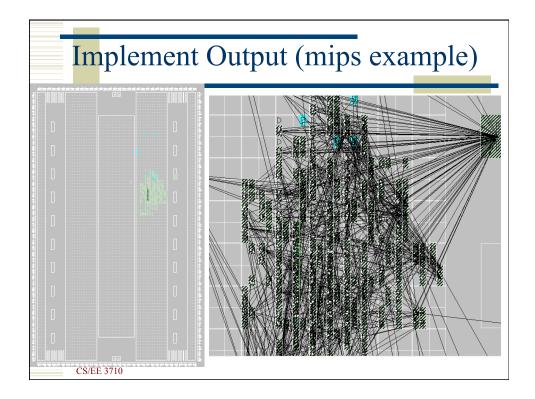

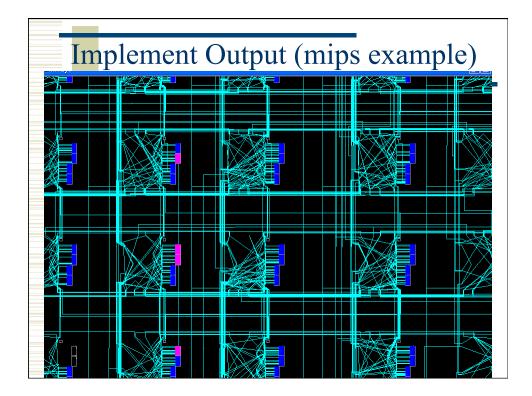

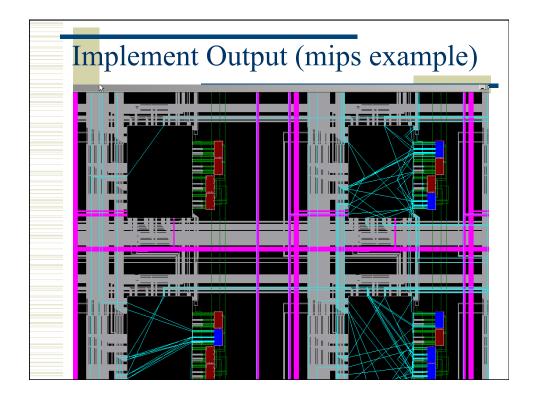

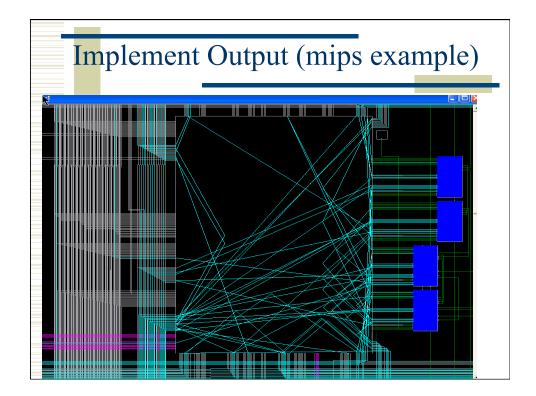

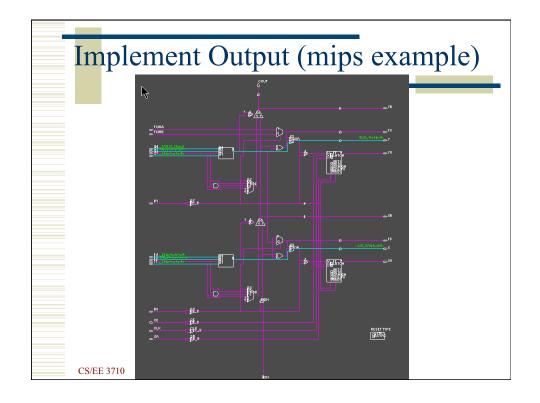

| Impl       | ement | Outpu | ıt                         | (m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nip | )S | e | X | a | m | p | le | ) |

|------------|-------|-------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|---|---|---|---|---|----|---|

|            |       |       | D<br>D<br>D<br>D<br>D<br>D | 1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 |     |    |   |   |   |   |   |    |   |

| CS/EE 3710 |       |       |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |    |   |   |   |   |   |    |   |

| ASIC                                                                                                  | vs. FPGA                                                                         |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                                                                                       |                                                                                  |

|                                                                                                       |                                                                                  |

| FPGA & ASIC Design Advantages                                                                         |                                                                                  |

| FPGA Design Advantages                                                                                | ASIC Design Advantages                                                           |

| Faster time-to-market - no layout, masks or other manufacturing<br>steps are needed                   | Full custom capability - for design since device is manufactured to design specs |

| <b>No upfront NRE</b> (non recurring expenses) - costs typically<br>associated with an ASIC design    | Lower unit costs - for very high volume designs                                  |

| Simpler design cycle - due to software that handles much of the<br>routing, placement, and timing     | Smaller form factor - since device is manufactured to design specs               |

| More predictable project cycle - due to elimination of potential re-<br>spins, wafer capacities, etc. | Higher raw internal clock speeds                                                 |

| Field reprogramability - a new bitstream can be uploaded<br>remotely                                  |                                                                                  |

|                                                                                                       |                                                                                  |

|                                                                                                       |                                                                                  |

|                                                                                                       |                                                                                  |

|                                                                                                       |                                                                                  |

|                                                                                                       |                                                                                  |

|                                                                                                       |                                                                                  |

|                                                                                                       |                                                                                  |

|                                                                                                       |                                                                                  |