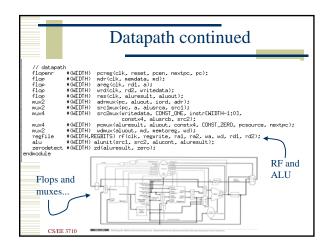

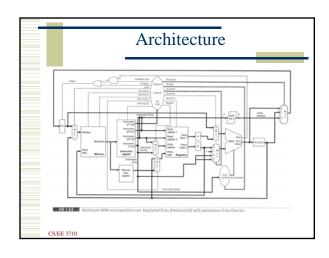

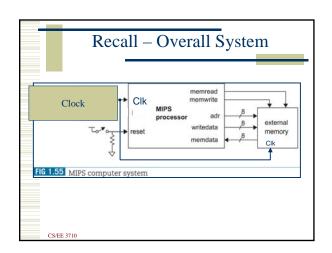

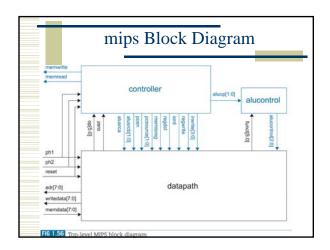

## Based on MIPS

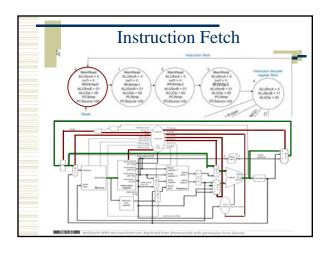

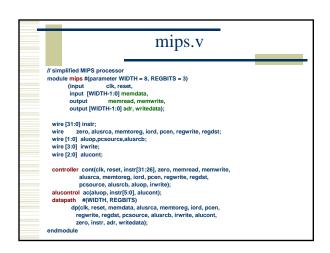

- In fact, it's based on the multi-cycle MIPS from Patterson and Hennessy

- Your CS/EE 3810 book...

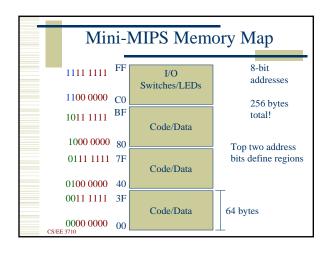

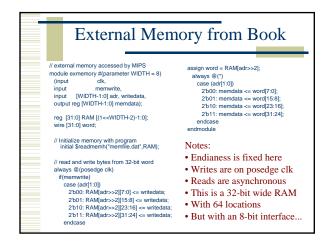

- 8-bit version

- 8-bit data and address

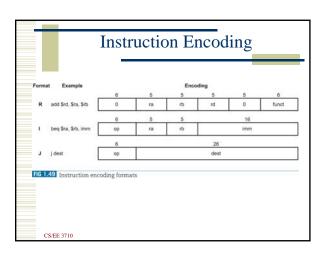

- 32-bit instruction format

- 8 registers numbered \$0-\$7

- \$0 is hardwired to the value 0

CS/EE 371

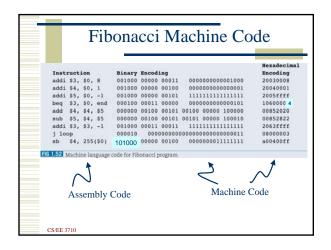

```

Instruction Set

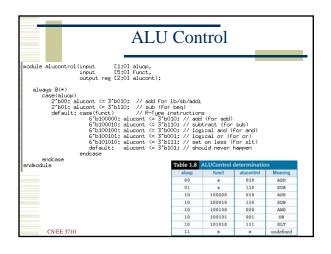

Table 1.7 MIP

add $1, $2, $3

addition:

$1 <- $2 + $3

000000

100000

sub $1, $2, $3

$1 <- $2 - $3

000000

100010

and $1, $2, $3

bitwise and:

$1 <- $2 and $3

000000

100100

$1 <- 1 if $2 < $3

$1 <- 0 otherwise

slt $1, $2, $3

set less than:

000000

101010

$1 <- $2 + imm

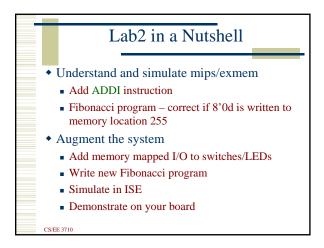

addi $1, $2, imm

add immediate:

001000

beq $1, $2, imm

000100

branch if equal:

PC <- PC + imm<sup>a</sup>

n/a

j destination

000010

n/a

100000

sb $1, imm($2) store byte:

mem[$2 + imm] <- $1

101000

. Technically, MIPS addresses specify bytes. Instructions require a four-byte word and must begin at addresses multiple of four. To most effectively use instruction bits in the full 32-bit MIPS architecture, branch and jump are specified in words and must be multiplied by four chiffred left two bits to be converted to byte addresses.

```

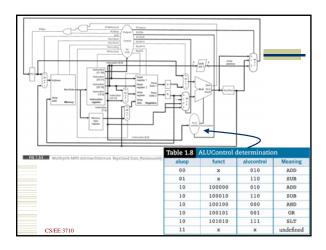

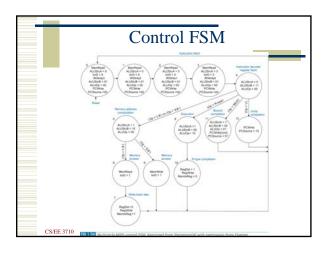

```

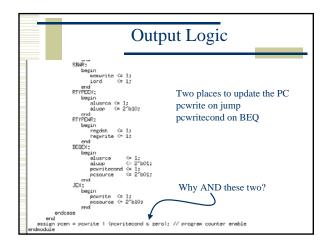

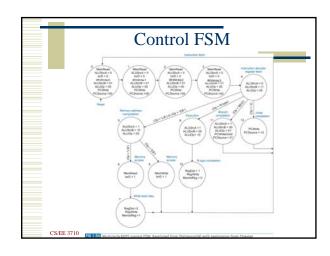

Output Logic

| Solvage 8(+) | Degin | Solvage | Solvage | Solvage 8(+) | Degin | Solvage 8(+) |

```